CIRCC Ver la hoja de datos (PDF) - SMSC -> Microchip

Número de pieza

componentes Descripción

Lista de partido

CIRCC Datasheet PDF : 70 Pages

| |||

NAME

CLK

RESET

CIR_PME

Power Down

DMAEN

IRQEN

nACE

nSCE

VCC

GND

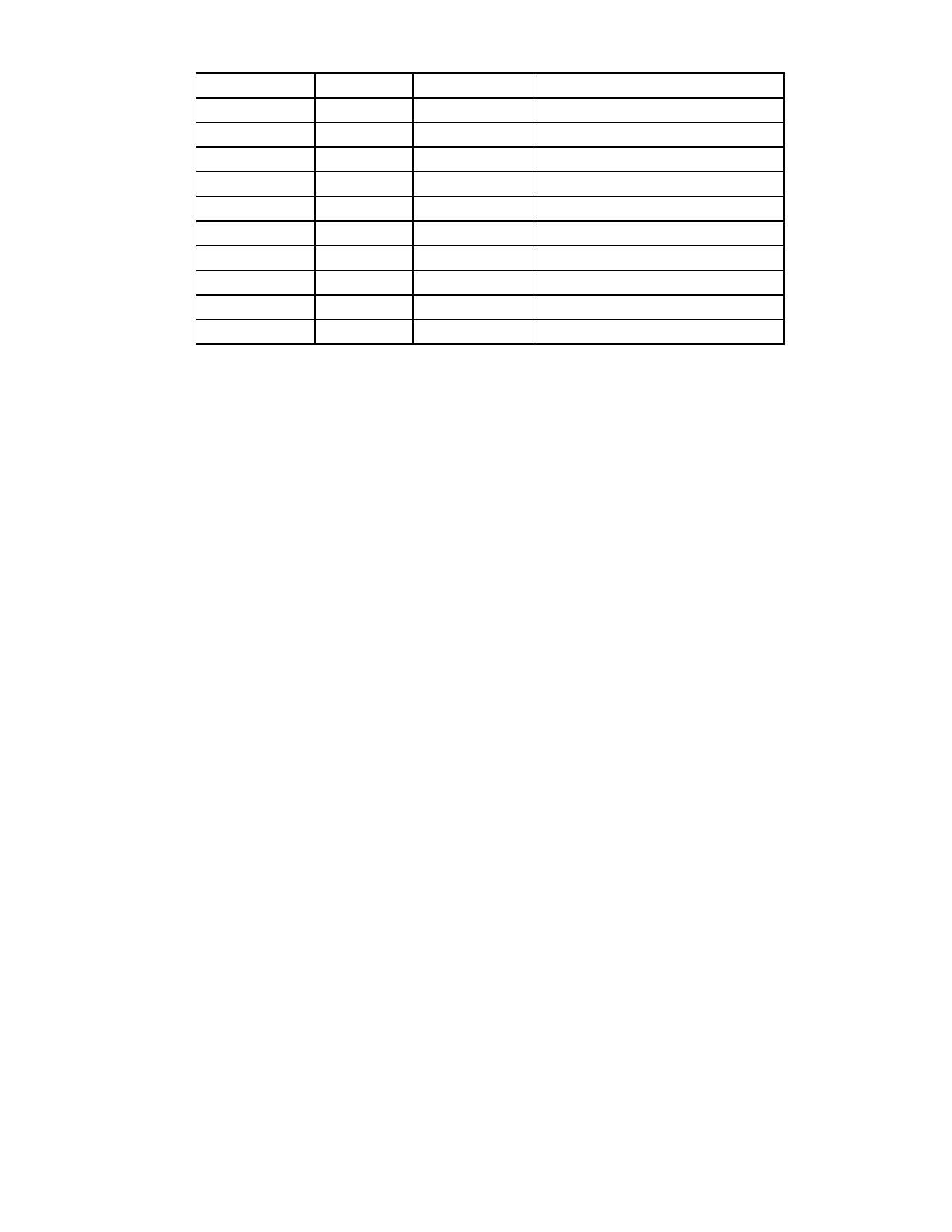

Table 5 - SYSTEM Signals

SIZE (BITS)

TYPE

DESCRIPTION

1

Input

System Clock

1

Input

CIrCC System Reset

1

Output

CIR PME Wake Event

1

Input

Low Power Control

1

Output

DRQ Tristate Control

1

Output

IRQ Tristate Control

1

Input

ACE 550 Register Bank Select

1

Input

SCE Register Bank Select

Power

System Supply

Power

System Ground

DMAEN

DMAEN is used by the chip-level interface to

tristate the CIrCC DRQ output when the DMA

Enable bit is inactive. The DMA Enable bit is

located in SCE Configuration Register B, bit 0.

IRQEN

IRQEN is used by the chip-level interface to

tristate the CIrCC IRQ output when the OUT2 bit

is inactive. The OUT2 bit is located in 16C550A

MODEM Control Register.

Power Down

The Power Down pin is used by the chip-level

interface to put the SCE into low power mode.

Note: Power Down only forces the SCE into low

power mode. The ACE power down function is

not a part of this specification.

CIR_PME

CIR_PME is used by a chip-level interface to

indicate that a valid NEC control frame has been

received and a PME Wake event can be issued.

(See the PME WAKE bit in the Consumer IR

Control Register in SCE Register Block Two).

CHIP-LEVEL CONFIGURATION CONTROLS

The following signals come from chip-level

configuration registers. There are two types of

Chip-Level Configuration Controls: CIrCC-

Specific controls, and Legacy Controls. Both

types have equivalent controls in either the

CIrCC ACE or SCE Registers.

The CIrCC-Specific controls have been newly

added primarily to support the CIrCC block.

Provisions have been made in new chip-level

configuration contexts to accommodate these

signals.

The Legacy controls already exist in other

contexts. Provisions have been made in legacy

devices to accommodate these controls from

either the Chip-Level Configuration Registers or

the CIrCC Registers; i.e., the last updated value

from either source determines the current control

state and is visible in both registers.

7