CDB6420 Ver la hoja de datos (PDF) - Cirrus Logic

Número de pieza

componentes Descripción

Lista de partido

CDB6420 Datasheet PDF : 52 Pages

| |||

CS6420

stage allows gains of 0 dB, 6 dB, 9.5 dB, and 12 dB

to be added prior to the ADC input. The default

gain stage setting is 0 dB.

The signal at APO should not exceed 2.8 Vpp at the

default gain stage setting. If other gain stages are

used then the full-scale signal at APO must also

change. Table 1 shows full-scale voltages as mea-

sured at APO for given programmable gains:

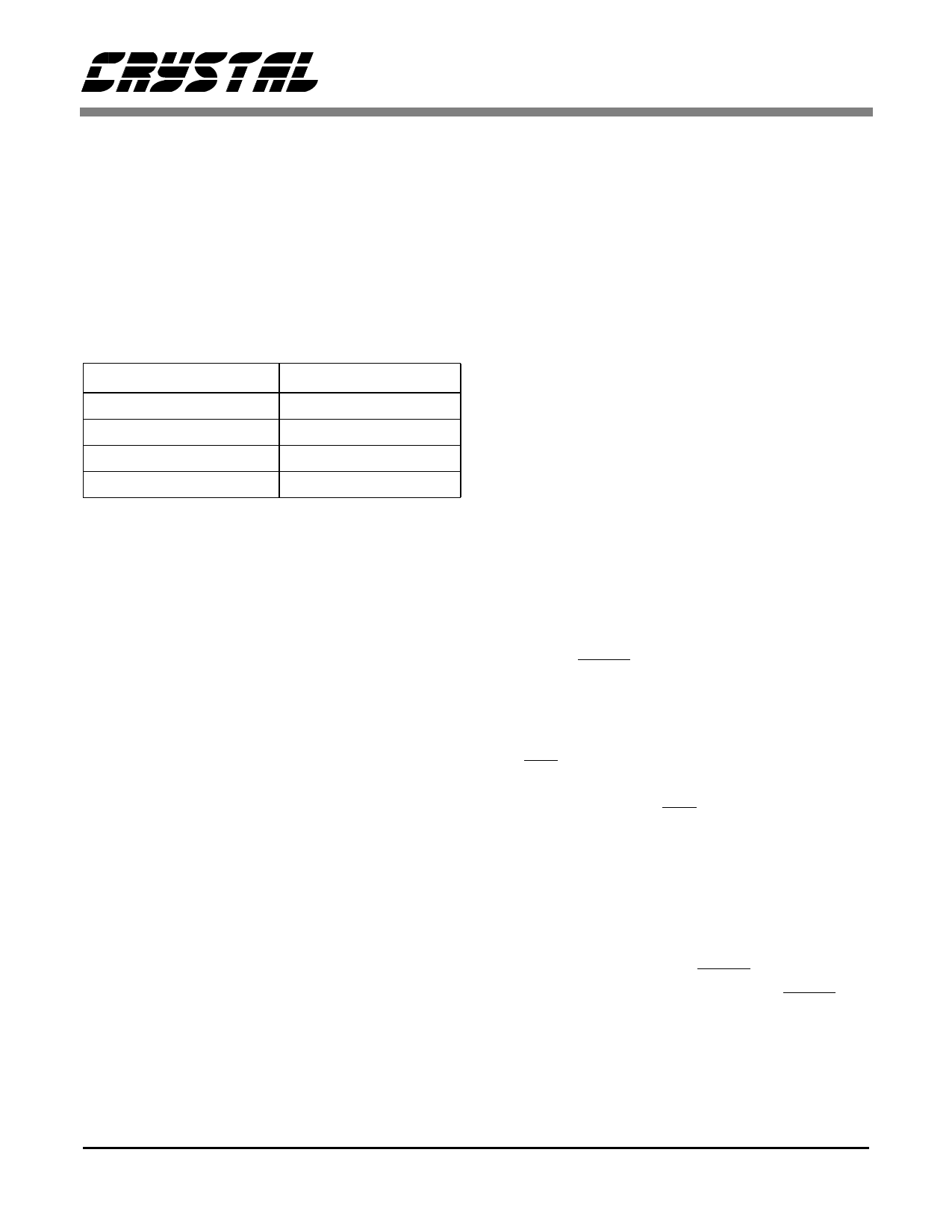

Gain Setting

0 dB

6 dB

9.5 dB

12 dB

Full-scale Voltage

2.8 Vpp

1.4 Vpp

0.94 Vpp

0.71 Vpp

Table 1. Full scale voltages for each gain stage.

MB provides a stable 3.5 VDC output from the on-

board voltage reference of the CS6420. MB may

not be connected to any load. MB serves to provide

decoupling for the internal 2.12 VDC bandgap ref-

erence, and must have a 0.1 µF and a 10 µF capac-

itor to ground for bypass. Noise on MB will

strongly influence the overall analog perfor-

mance of the CS6420.

The acoustic output, AO, should connect to a sin-

gle-pole low-pass RC network with a corner fre-

quency of 4 kHz, which will filter out-of-band

components. The maximum voltage swing at AO is

2.8 Vpp. AO is capable of driving down to a 10 kΩ

load.

Network Interface

The pins NI (pin 17) and NO (pin 4) make up the

Network Interface. The details of the Network In-

terface are shown in Figure 4.

NI is the input from the telephone network side into

the CS6420. The signal into NI must be low pass

filtered by a single-pole RC filter with a corner fre-

quency of 8 kHz.

A programmable analog gain stage (PGA) accessi-

ble through the Microcontroller Interface amplifies

signals received at NI. This gain stage allows gains

of 0 dB, 6 dB, 9.5 dB, and 12 dB to be added prior

to the ADC input. The default gain stage setting for

the network side is 0 dB.

The signal at NI should not exceed 2.8 Vpp at the

default gain stage setting. If other gain stages are

used then the full-scale signal at NI must also

change. Table 1 shows full-scale voltages as mea-

sured at NI for given programmable gains.

The output to the telephone network side, NO,

should connect to a single pole RC network with a

corner frequency at 4 kHz, which will filter out-of-

band components. The maximum swing NO is ca-

pable of producing is 2.8 Vpp. NO is capable of

driving down to a 10 kΩ load.

Microcontroller Interface

Several control functions of the CS6420 are acces-

sible through its Microcontroller Interface, which

consists of three pins: DATA (pin 8), STROBE

(pin 7), and DRDY (pin 6). These inputs are intend-

ed to connect to the outputs of a microcontroller to

allow write-only access to the 16-bit Microcontrol-

ler Control Register (MCR).

The RST (pin 5) pin, which affects the entire inte-

grated circuit, is especially significant to the Micro-

controller Interface. RST is used to place the

CS6420 into a known state of operation. Two sub-

types of reset are possible: cold reset and warm re-

set.

Description

The Microcontroller Interface is implemented by a

serial shift register gated by DRDY. The microcon-

troller begins the transaction by setting DRDY low

and STROBE low. The most significant bit (MSB),

Bit 15, of the 16-bit data word should be presented

to the DATA pin and then STROBE should be

brought high to shift the data bit into the CS6420.

STROBE should be brought low again so it is ready

10

DS205PP2