FCT162511AT Ver la hoja de datos (PDF) - Integrated Device Technology

Número de pieza

componentes Descripción

Lista de partido

FCT162511AT Datasheet PDF : 11 Pages

| |||

IDT54/74FCT162511AT/CT

FAST CMOS 16-BIT REGISTERED/LATCHED TRANSCEIVER WITH PARITY

MILITARY AND COMMERCIAL TEMPERATURE RANGES

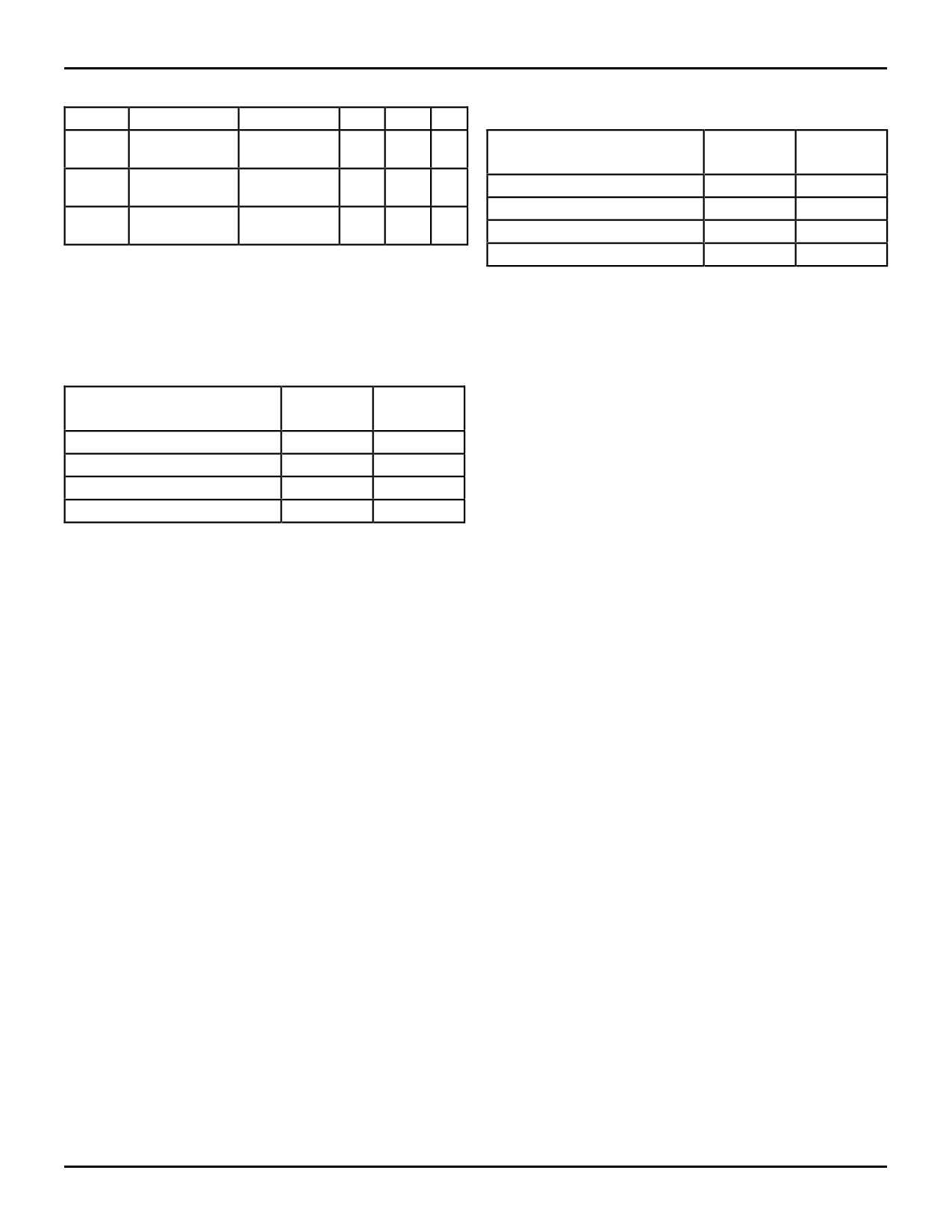

CAPACITANCE (TA = +25°C, f = 1.0MHz)

Symbol Parameter(1) Conditions Typ. Max. Unit

CIN

Input

VIN = 0V

3.5 6.0 pF

Capacitance

CI/O

I/O

VOUT = 0V 3.5 8.0 pF

Capacitance

CO

Open Drain

VOUT = 0V 3.5 6.0 pF

Capacitance

NOTE:

2916 lnk 04

1. This parameter is measured at characterization but not tested.

FUNCTION TABLE

(PARITY CHECKING)(1, 2, 3, 4)

A0 - A7 and PA1(5), Total Number

of inputs that are high

ODD/EVEN

PERB

1, 3, 5, 7 or 9

1, 3, 5, 7 or 9

0, 2, 4, 6 or 8

L

L

H

H(6)

L

H(6)

0, 2, 4, 6 or 8

H

L

NOTES:

2916 tbl 05

1. Conditions shown are for GEN/CHK = H, OEAB = L, OEBA = H.

2. A-to-B parity checking is shown. B-to-A parity checking is similar but uses

OEBA = L, OEAB = H and errors will be indicated on PERA.

3. In parity checking mode the parity bits will be transmitted unchanged along

with the corresponding data regardless of parity errors. (PB1 = PA1).

4. The response shown is for LEAB = H. If LEAB = L then CLKAB will control

as an edge triggered clock.

5. Conditions shown are for the byte A0-A7 and PA1. The byte A8-A15 and

PA2 is similiar.

6. The parity error flag PERB is a combined flag for both bytes A0-A7 and A8-

A15. If a parity error occurs on either byte PERB will go low. PERB is an

open drain output which must be externally pulled up to achieve a logic

HIGH.

FUNCTION TABLE

(PARITY GENERATION)(1, 2, 3, 4, 5)

A0 - A7, Total Number

of inputs that are high

ODD/EVEN

PB1

1, 3, 5 or 7

L

H

1, 3, 5 or 7

H

L

0, 2, 4, 6 or 8

L

L

0, 2, 4, 6 or 8

H

H

NOTES:

2916 tbl 06

1. Conditions shown are for GEN/CHK = L, OEAB = L, OEBA = H.

2. A-to-B parity checking is shown. B-to-A is capable of parity checking while

A-to-B is performing generation. B-to-A will not generate parity.

3. The response shown is for LEAB = H. If LEAB = L then CLKAB will control

as an edge triggered clock.

4. Conditions shown are for the byte A0-A7 . The byte A8-A15 is similiar but

will output the parity on PB2.

5. The error flag PERB will remain in a high state during parity generation.

5.11

5