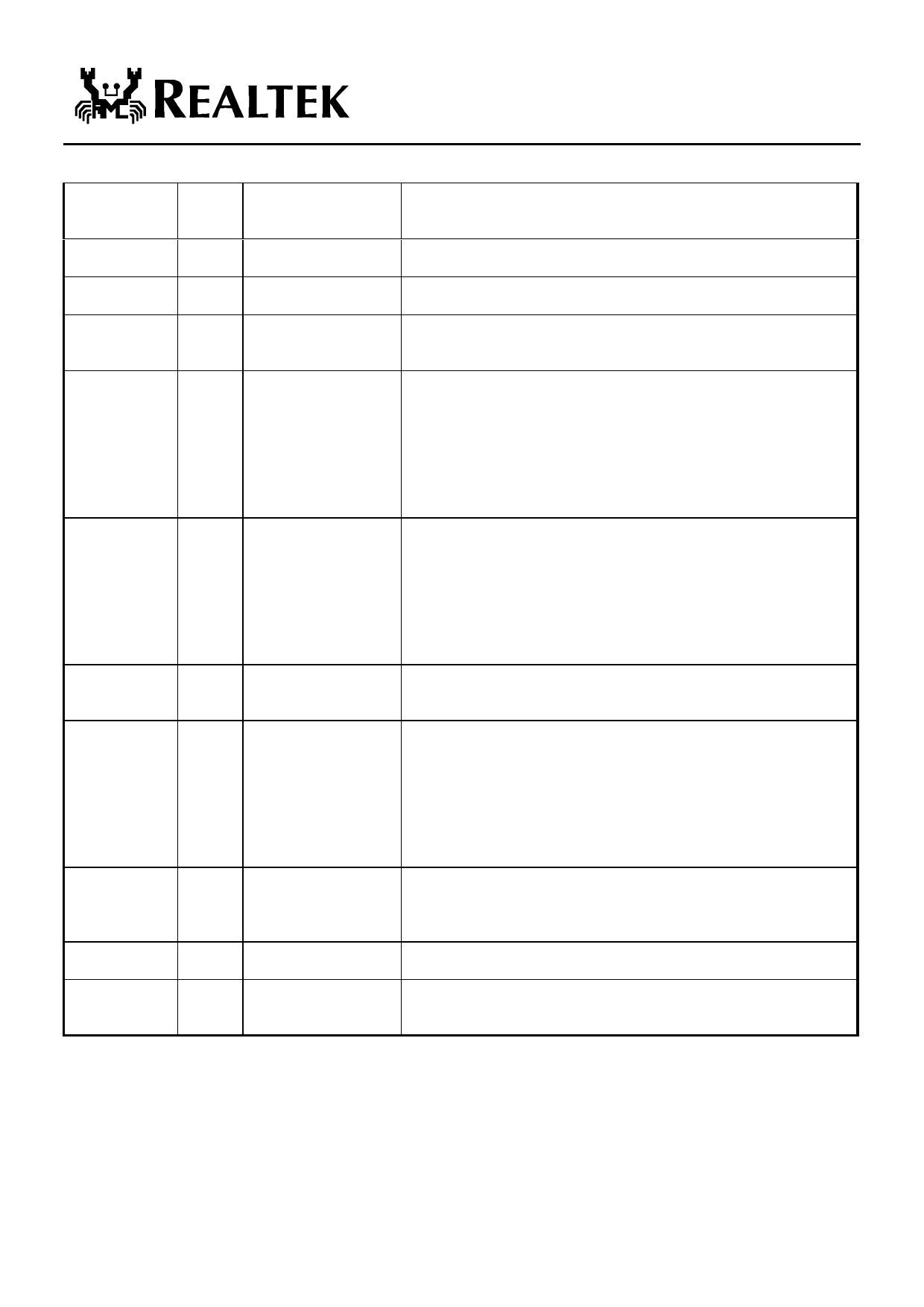

RTL8100 Ver la hoja de datos (PDF) - Unspecified

Número de pieza

componentes Descripción

Lista de partido

RTL8100 Datasheet PDF : 58 Pages

| |||

GNTB

REQB

IDSEL

INTAB

IRDYB

I

T/S

I

O/D

S/T/S

TRDYB

S/T/S

PAR

PERRB

T/S

S/T/S

SERRB

STOPB

RSTB

O/D

S/T/S

I

RTL8100B(L)

84

Grant: This signal is asserted low to indicate to the RTL8100B(L) that

the central arbiter has granted ownership of the bus to the RTL8100B

(L). This input is used when the RTL8100B(L) is acting as a bus master.

85

Request: The RTL8100B(L) will assert this signal low to request the

ownership of the bus from the central arbiter.

99

Initialization Device Select: This pin allows the RTL8100B(L) to

identify when configuration read/write transactions are intended for it.

81

INTAB: Used to request an interrupt. It is asserted low when an

interrupt condition occurs, as defined by the Interrupt Status, Interrupt

Mask and Interrupt Enable registers.

13

Initiator Ready: This indicates the initiating agent’s ability to complete

the current data phase of the transaction.

As a bus master, this signal will be asserted low when the

RTL8100B(L) is ready to complete the current data phase transaction.

This signal is used in conjunction with the TRDYB signal. Data

transaction takes place at the rising edge of CLK when both IRDYB and

TRDYB are asserted low. As a target, this signal indicates that the

master has put data on the bus.

14

Target Ready: This indicates the target agent’s ability to complete the

current phase of the transaction.

As a bus master, this signal indicates that the target is ready for the data

during write operations and with the data during read operations. As a

target, this signal will be asserted low when the (slave) device is ready

to complete the current data phase transaction. This signal is used in

conjunction with the IRDYB signal. Data transaction takes place at the

rising edge of CLK when both IRDYB and TRDYB are asserted low.

20

Parity: This signal indicates even parity across AD31-0 and C/BE3-0

including the PAR pin. As a master, PAR is asserted during address and

write data phases. As a target, PAR is asserted during read data phases.

18

Parity Error: When the RTL8100B(L) is the bus master and a parity

error is detected, the RTL8100B(L) asserts both SERR bit in ISR and

Configuration Space command bit 8 (SERRB enable). Next, it

completes the current data burst transaction, then stops operation and

resets itself. After the host clears the system error, the RTL8100B(L)

continues its operation.

When the RTL8100B(L) is the bus target and a parity error is detected,

the RTL8100B(L) asserts this PERRB pin low.

19

System Error: If an address parity error is detected and Configuration

Space Status register bit 15 (detected parity error) is enabled,

RTL8100B(L) asserts both SERRB pin low and bit 14 of Status register

in Configuration Space.

17

Stop: Indicates the current target is requesting the master to stop the

current transaction.

82

Reset: When RSTB is asserted low, the RTL8100B(L) performs

internal system hardware reset. RSTB must be held for a minimum of

120 ns.

2001-11-9

7

Rev.1.41