UT84520 Ver la hoja de datos (PDF) - Unisonic Technologies

Número de pieza

componentes Descripción

Lista de partido

UT84520 Datasheet PDF : 13 Pages

| |||

UTC UT84520

CMOS IC

C) PS/2 mouse Data Transmission:

a) UT84520 generates the clocking signal when sending data to and receiving data from the system.

b) The system requests UT84520 receive system data output by forcing the DATA line to an inactive level and

allowing CLK line to go to an active level.

c) Data transmission frame

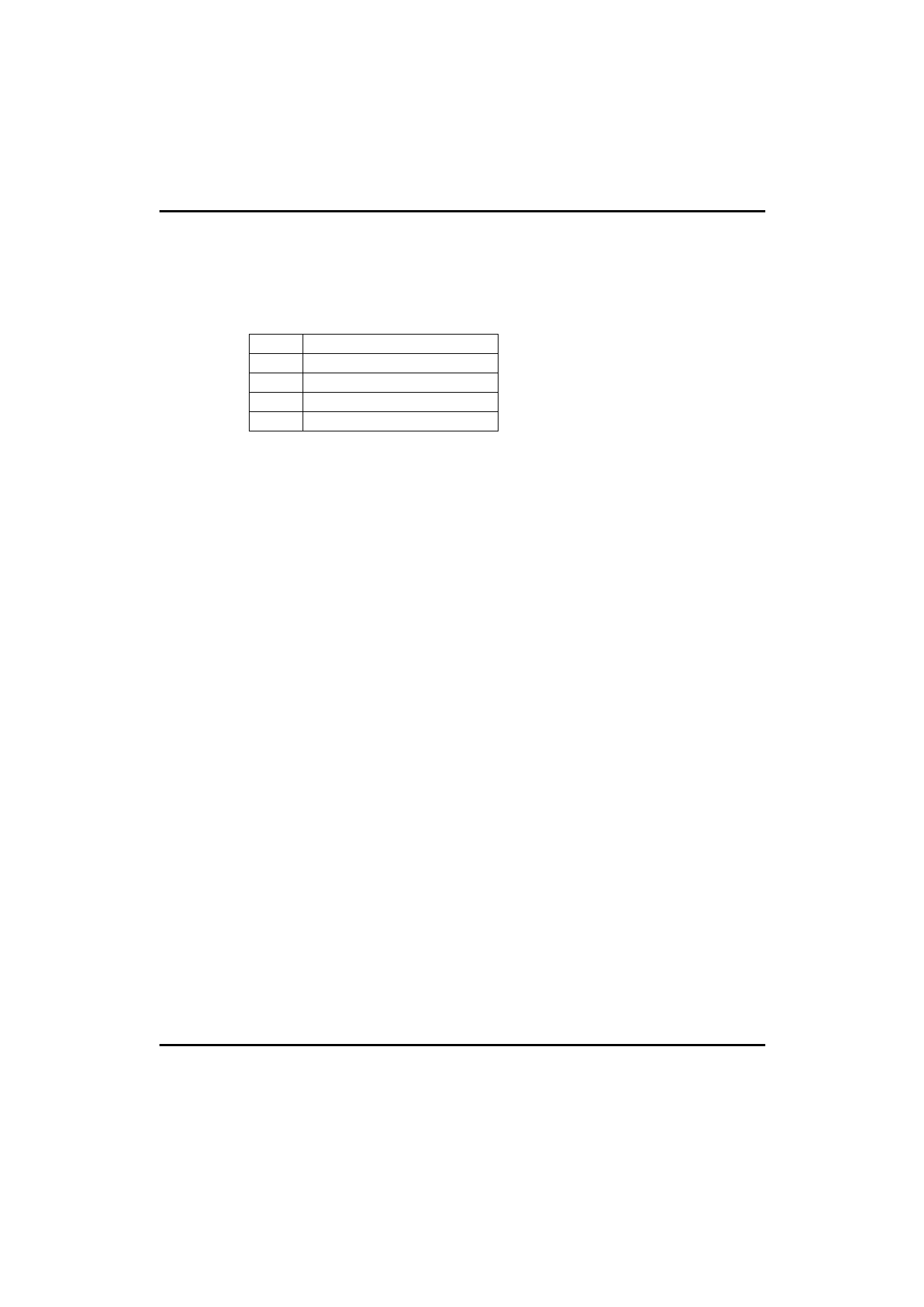

Bit

Funtion

1 Start bit( always 0 )

2-9 Data bits (D0-D7 )

10 Parity bit (odd parity)

11 Stop bit (always 1)

d). Data Output (data from UT84520 to system )

If CLK is low (inhibit status), data is no transmission.

If CLK is high and DATA is low (request-to-send), data is updated. Data is received from the system and no

transmission are stared by UT84520 until CLK and DATA both high.

If CLK and DATA both are high, the transmission is ready. DATA is valid prior to the falling edge of CLK and

beyond the rising edge of CLK. During transmission, UT84520 check for line contention by checking for an

inactive level on CLK at intervals not to exceed l00u sec Contention occurs when the system lowers CLK to

inhibit UT84520 output after UT84520 has started a transmission. If this occurs before the rising edge of the

tenth clock, UT84520 internally store its data in its buffer and returns DATA and CLK to an active level. If the

contention does not occur by the tenth clock, the transmission is complete.

Following a transmission the system inhibits UT84520 by holding CLK low until it service the input or until the

system receives a request to send a response from UT84520.

e).Data Input (from system to UT84520 )

The system first check if UT84520 is transmitting data. If UT84520 is transmitting, the system can override the

output forcing CLK to an inactive level prior to the tenth clock. If UT84520 transmission is beyond the tenth clock,

the system receives the data. If UT84520 is not transmitting or if the system choose to override the output, the

system force CLK to an inactive level for a period of not less than 100u sec while preparing for output. When the

system is ready to output start bit (0), it allows CLK go to active level. lf

request-to-send is detected UT84520 clocks 11 bits. Following the tenth clock UT84520 checks for an active l

evel on the DATA line, and if found, force

DATA low, and clock once more. If occurs framing error, UT84520 continue to clock until DATA is high, then

clocks the line control bit and request a Resend. When the system sends out a command or data transmission

that requires a response, the system waits for UT84520 to respond before sending its next output.

D).PS/2 Mouse Error Handling

a). A Resend command (FE ) following receipt of an invalid input or any input with incorrect parity

b). If two invalid input are received in succession, an error code of hex (FC) is send to the system.

c).The counter accumulators are cleared after receiving any command except ”Resend”.

d). UT84520 receives a Resend command (FE),it transmit its last packet of data

e). ln the stream mode "Resend" is received by UT84520 following a 3-byte data packet transmission to the

system. UT84520 resend the 3-byte data packet prior to clearing the counter.

UTC UNISONIC TECHNOLOGIES CO., LTD. 9

QW-R502-004,A