CS48LV13CNZR Ver la hoja de datos (PDF) - Cirrus Logic

Número de pieza

componentes Descripción

Lista de partido

CS48LV13CNZR Datasheet PDF : 26 Pages

| |||

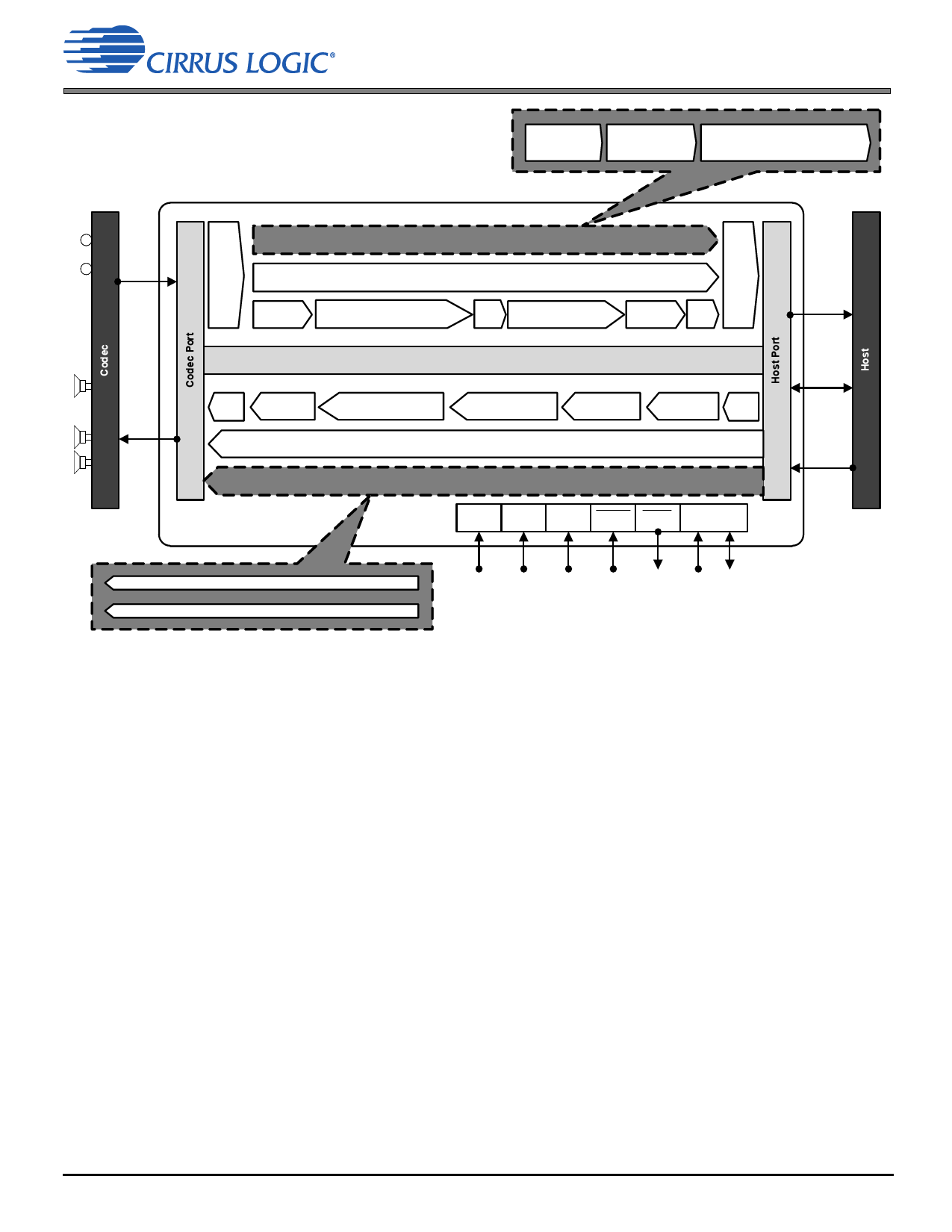

3.1 Cirrus Logic 32-bit DSP Core

Voice Activity SoundClear

Sensory Inc.

Detector

ASR Enhance™ TrulyHandsfree™ Voice Control

I2S

Raw

PCM

I2S

Clean

PCM

Near

End

Optional Voice Processing Features

PGA

SoundClear ASR Enhance™

Noise

Acoustic Echo Canceller

Reduction Residual Echo Suppressor

NLP

Spectrally Matched

Comfort Noise

PGA

Dynamic

FlexEQ

ALC

Full-Duplex Control+ Voice Activity Detection+ Double-Talk Detection

PGA

Comfort

Noise

Automatic Volume

Control

Automatic Level

Control

Advanced Media Processor

Dynamic

FlexEQ

Noise

Reduction

PGA

Optional Postprocessing Features

GND

VD

VL RESET BUSY PLL/ClkMgr

I2S

Clean

PCM

SPI/I2C

I2S

Raw

PCM

Far

End

Dolby Laboratories, Inc. Audio Postprocessing Algorithms

DTS, Inc. Audio Postprocessing Algorithms

Figure 3-2. CS48LV13 Block Diagram

3.1 Cirrus Logic 32-bit DSP Core

The core is a high-performance, 32-bit, fixed-point DSP that is capable of performing two multiply-and-accumulate (MAC)

operations per clock cycle. The core has eight 72-bit accumulators, four X- and four Y-data registers, and 12 index

registers. It can operate up to 130 MHz, depending on mode and concurrency requirements, but it may also operate at low

speed to support specialized low-power modes, such as always-on voice wake.

The DSP core is coupled to a flexible DMA engine. The DMA engine can move data between peripherals such as the

multi-channel serial audio port, or any DSP core memory, without the intervention of the DSP. The DMA engine off-loads

data move instructions from the DSP core, leaving more MIPS available for signal-processing instructions.

3.2 Processing Groups

Providing consistent high-quality Tx and Rx voice streams in constantly changing environments requires a complex data

flow with constant interaction between various functional modules. While the actual data flow is more complex and not

linear, the architecture can be approximated as a set of in-line processing groups or chains that operate in different modes

depending on the current use model as follows.

CS48LV12:

1. Tx Voice DSP Chain

2. Rx Voice DSP Chain

3. Voice DSP Control and Detection

4. Audio Playback DSP Chain

7

DS1057F1