M68AW127BM10NK6 Ver la hoja de datos (PDF) - STMicroelectronics

Número de pieza

componentes Descripción

Lista de partido

M68AW127BM10NK6 Datasheet PDF : 20 Pages

| |||

M68AW127B

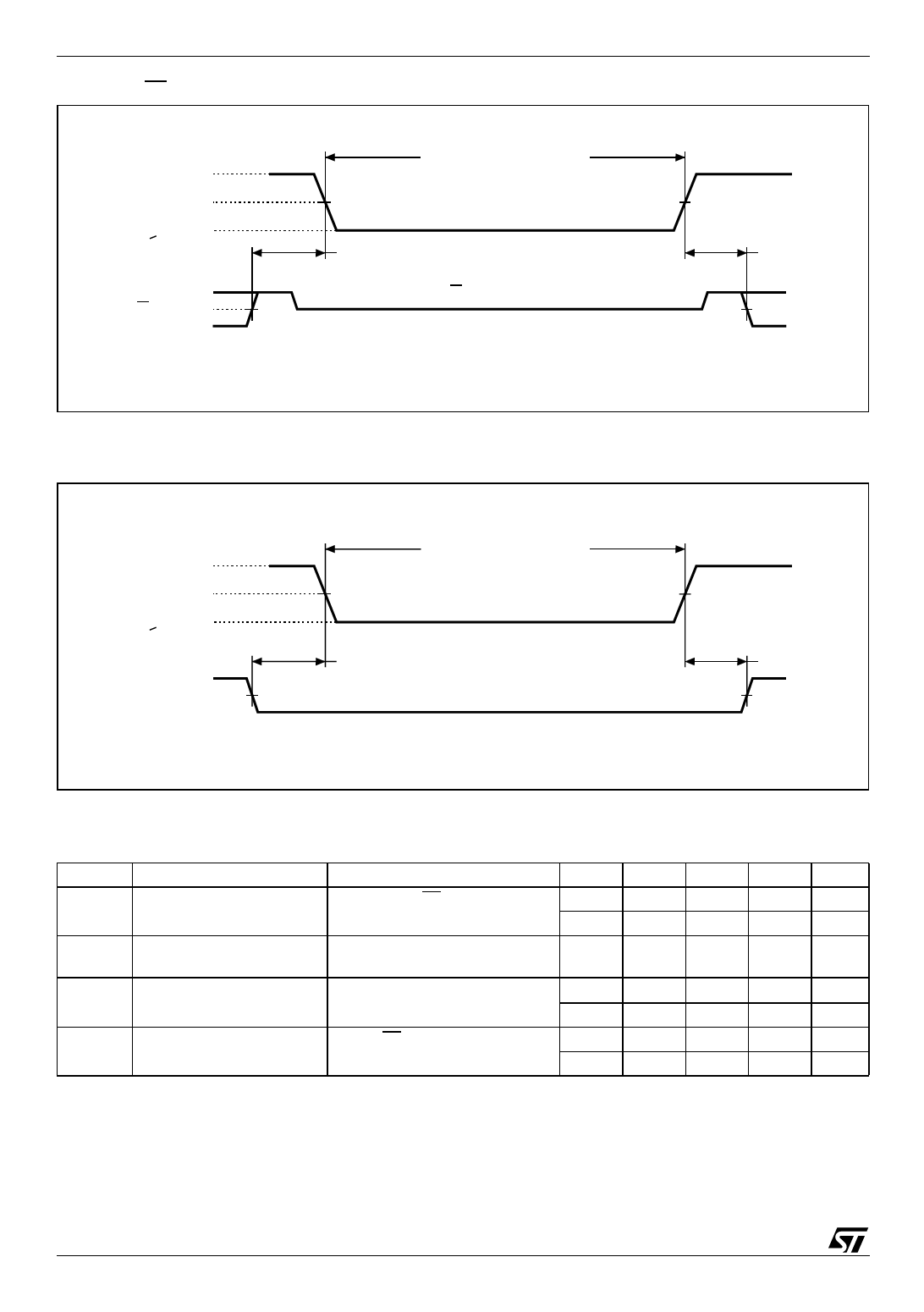

Figure 13. E1 Controlled, Low VCC Data Retention AC Waveforms

3.6V

VCC

2.7V

VDR > 1.5V (1)

E1

DATA RETENTION MODE

tCDR

E1 ≥ VDR – 0.2V

Note: 1. For 100ns speed class VDR ≥ 2.0V.

Figure 14. E2 Controlled, Low VCC Data Retention AC Waveforms

tR

AI05980

3.6V

VCC

2.7V

VDR > 1.5V (1)

E2

DATA RETENTION MODE

tCDR

E2 ≤ 0.2V

tR

AI05957B

Note: 1. For 100ns speed class VDR ≥ 2.0V.

Table 9. Low VCC Data Retention Characteristics

Symbol

Parameter

Test Condition

Min Typ

ICCDR (1)

Supply Current

(Data Retention)

VCC = 1.5V, E1 ≥ VCC –0.2V or 70

E2 ≤ 0.2V, f = 0

100

tCDR (1,2)

Chip Deselected to Data

Retention Time

0

tR (2) Operation Recovery Time

70

tAVAV

100

5

VDR (1)

Supply Voltage

(Data Retention)

E1 ≥ VCC –0.2V or

E2 ≤ 0.2V, f = 0

70

1.5

100

2.0

Note: 1. All other Inputs at VIH ≥ VCC –0.2V or VIL ≤ 0.2V.

2. Tested initially and after any design or process that may affect these parameters. tAVAV is Read cycle time.

3. No input may exceed VCC +0.2V.

Max

4.5

5

Unit

µA

µA

ns

ns

ms

V

V

14/20