A29DL322UV-80 Ver la hoja de datos (PDF) - AMIC Technology

Número de pieza

componentes Descripción

Lista de partido

A29DL322UV-80

A29DL322UV-80 Datasheet PDF : 50 Pages

| |||

A29DL32x Series

GENERAL DESCRIPTION

The A29DL32x family consists of 32 megabit, 3.0 volt-only

flash memory devices, organized as 2,097,152 words of 16

bits each or 4,194,304 bytes of 8 bits each. Word mode data

appears on I/O0–I/O15; byte mode data appears on I/O0–I/O7.

The device is designed to be programmed in-system with the

standard 3.0 volt VCC supply, and can also be programmed

in standard EPROM programmers.

The device is available with an access time of 70, 80, 90, or

120 ns. The devices are offered in 48-pin TSOP and 48-ball

Fine-pitch TFBGA. Standard control pins—chip enable ( CE ),

write enable ( WE ), and output enable ( OE )—control

normal read and write operations, and avoid bus contention

issues.

The device requires only a single 3.0 volt power supply for

both read and write functions. Internally generated and

regulated voltages are provided for the program and erase

operations.

Simultaneous Read/Write Operations with Zero

Latency

The Simultaneous Read/Write architecture provides

simultaneous operation by dividing the memory space into

two banks. The device can improve overall system

performance by allowing a host system to program or erase

in one bank, then immediately and simultaneously read from

the other bank, with zero latency. This releases the system

from waiting for the completion of program or erase

operations.

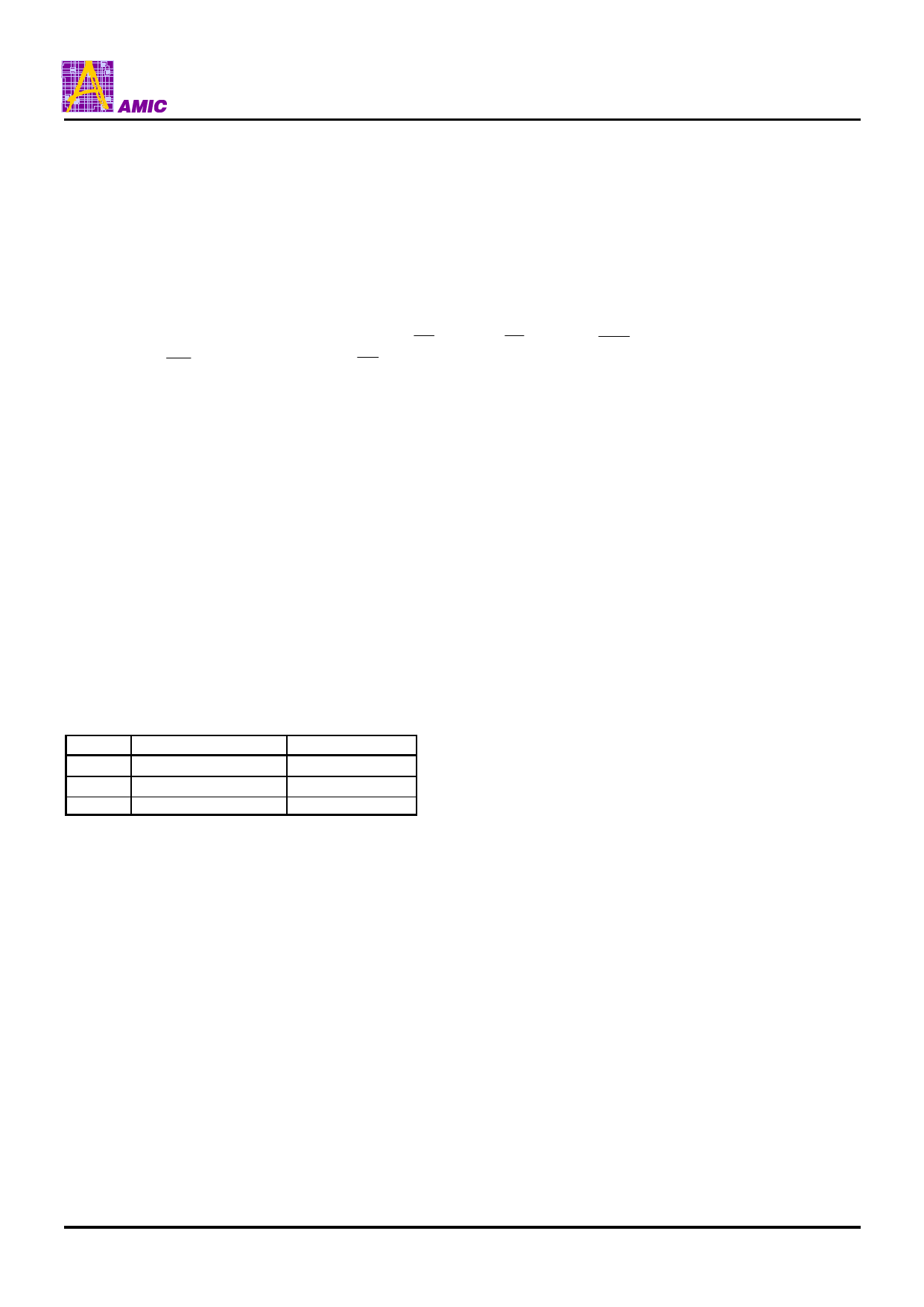

The A29DL32x devices use multiple bank architectures to

provide flexibility for different applications. Three devices are

available with these bank sizes:

Device

DL322

Bank 1

4 Mb

Bank 2

28 Mb

DL323

8 Mb

24 Mb

DL324

16 Mb

16 Mb

A29DL32x Features

The device offers complete compatibility with the JEDEC

single-power-supply Flash command set standard.

Commands are written to the command register using

standard microprocessor write timings. Reading data out of

the device is similar to reading from other Flash or EPROM

devices.

The host system can detect whether a program or erase

operation is complete by using the device status bits:

RY/ BY pin, I/O7 ( Data Polling) and I/O6/I/O2 (toggle bits).

After a program or erase cycle has been completed, the

device automatically returns to reading array data.

The sector erase architecture allows memory sectors to be

erased and reprogrammed without affecting the data

contents of other sectors. The device is fully erased when

shipped from the factory.

Hardware data protection measures include a low VCC

detector that automatically inhibits write operations during

power transitions. The hardware sector protection feature

disables both program and erase operations in any

combination of the sectors of memory. This can be achieved

in-s y s t e m or via programming equipment.

The device offers two power-saving features. When

addresses have been stable for a specified amount of time,

the device enters the automatic sleep mode. The system

can also place the device into the standby mode. Power

consumption is greatly reduced in both modes.

PRELIMINARY (May, 2005, Version 0.0)

2

AMIC Technology, Corp.