A43L0616AV-6 Ver la hoja de datos (PDF) - AMIC Technology

Número de pieza

componentes Descripción

Lista de partido

A43L0616AV-6 Datasheet PDF : 45 Pages

| |||

A43L0616A

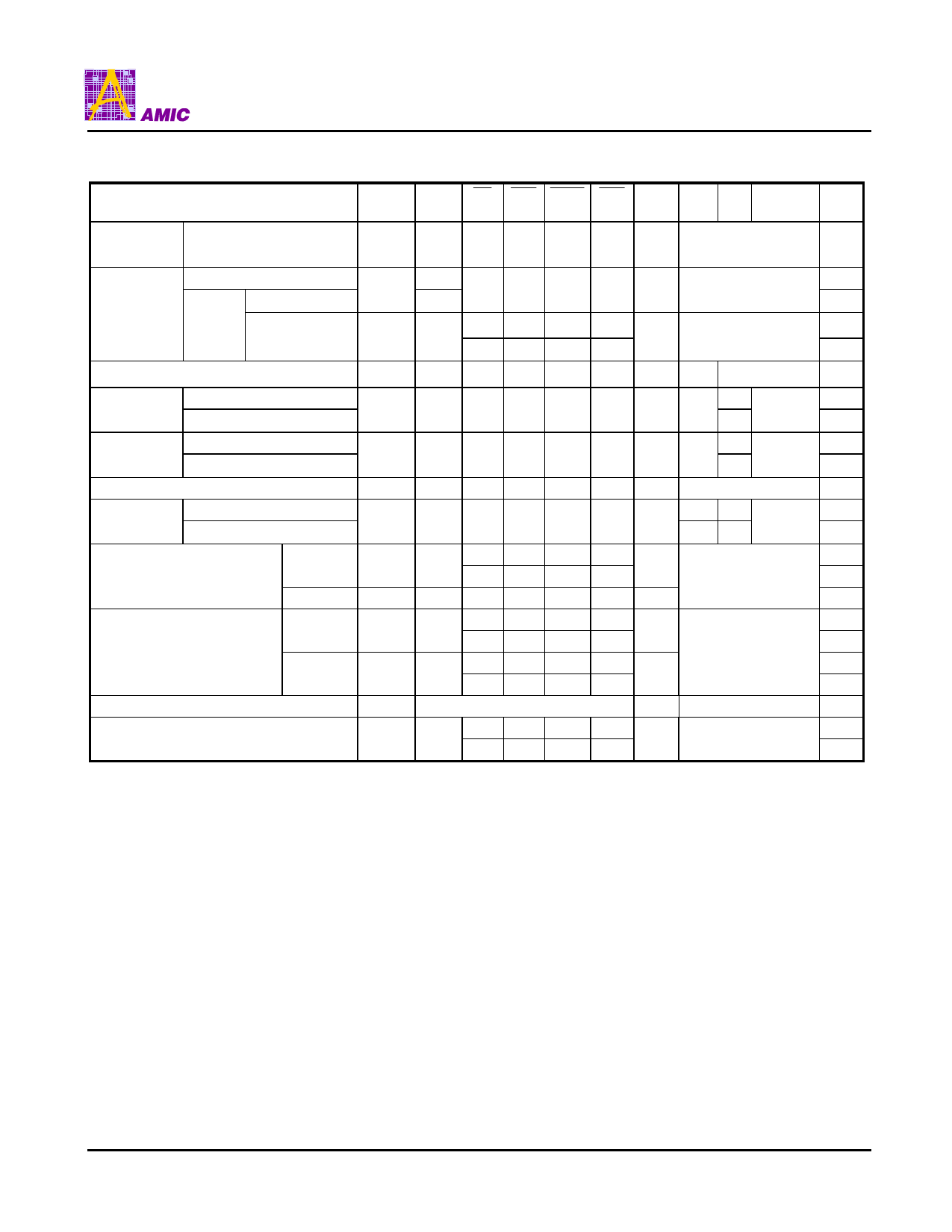

Simplified Truth Table

Register

Command

Mode Register Set

CKEn-1 CKEn CS RAS CAS WE DQM BA A10/ A9~A0 Notes

AP

H

X

LL

L

L

X

OP CODE

1,2

Refresh

Auto Refresh

Self

Refresh

Entry

Exit

Bank Active & Row Addr.

H

3

H

L

LL

L

H

X

X

3

LHH H

3

L

H

X

X

HX X X

3

H

X

LL

H

H

X V Row Addr.

4

Read &

Auto Precharge Disable

Column Addr. Auto Precharge Enable

Write &

Auto Precharge Disable

Column Addr. Auto Precharge Enable

Burst Stop

Precharge

Bank Selection

Both Banks

Clock Suspend or

Active Power Down

Entry

Exit

Precharge Power Down Mode

Entry

Exit

DQM

No Operation Command

L Column 4

H

X

LH

L

H

X V H Addr. 4,5

L Column 4

H

X

LH

L

L

X V H Addr. 4,5

H

X LHH L X

X

6

VL

H

X

LL

H

L

X XH

X

LHH H

H

L

X

HX X X

X

L

H XX X X X

LHH H

H

L

X

HX X X

X

LV V V

L

H

X

HX X X

H

X

V

X

7

LHH H

H

X

X

X

HX X X

(V = Valid, X = Don’t Care, H = Logic High, L = Logic Low)

Note : 1. OP Code : Operand Code

A0~A10/AP,BA : Program keys. (@MRS)

2. MRS can be issued only at both banks precharge state.

A new command can be issued after 2 clock cycle of MRS.

3. Auto refresh functions as same as CBR refresh of DRAM.

The automatical precharge without Row precharge command is meant by “Auto”.

Auto/Self refresh can be issued only at both precharge state.

4. BA : Bank select address.

If “Low” at read, write, Row active and precharge, bank A is selected.

If “High” at read, write, Row active and precharge, bank B is selected.

If A10/AP is “High” at Row precharge, BA is ignored and both banks are selected.

5. During burst read or write with auto precharge, new read write command cannot be issued.

Another bank read write command can be issued at every burst length.

6. Burst stop command is valid at every burst length.

7. DQM sampled at positive going edge of a CLK masks the data-in at the very CLK (Write DQM latency is 0),

but makes the data-out Hi-Z state after 2 CLK cycles. (Read DQM latency is 2)

(May, 2001, Version 1.0)

9

AMIC Technology, Inc.