BT8110 Ver la hoja de datos (PDF) - Unspecified

Número de pieza

componentes Descripción

Lista de partido

BT8110 Datasheet PDF : 84 Pages

| |||

1.0 Product Description

1.1 Channel Capacity and Configuration Modes

Bt8110/8110B

High-Capacity ADPCM Processor

1.1 Channel Capacity and Configuration Modes

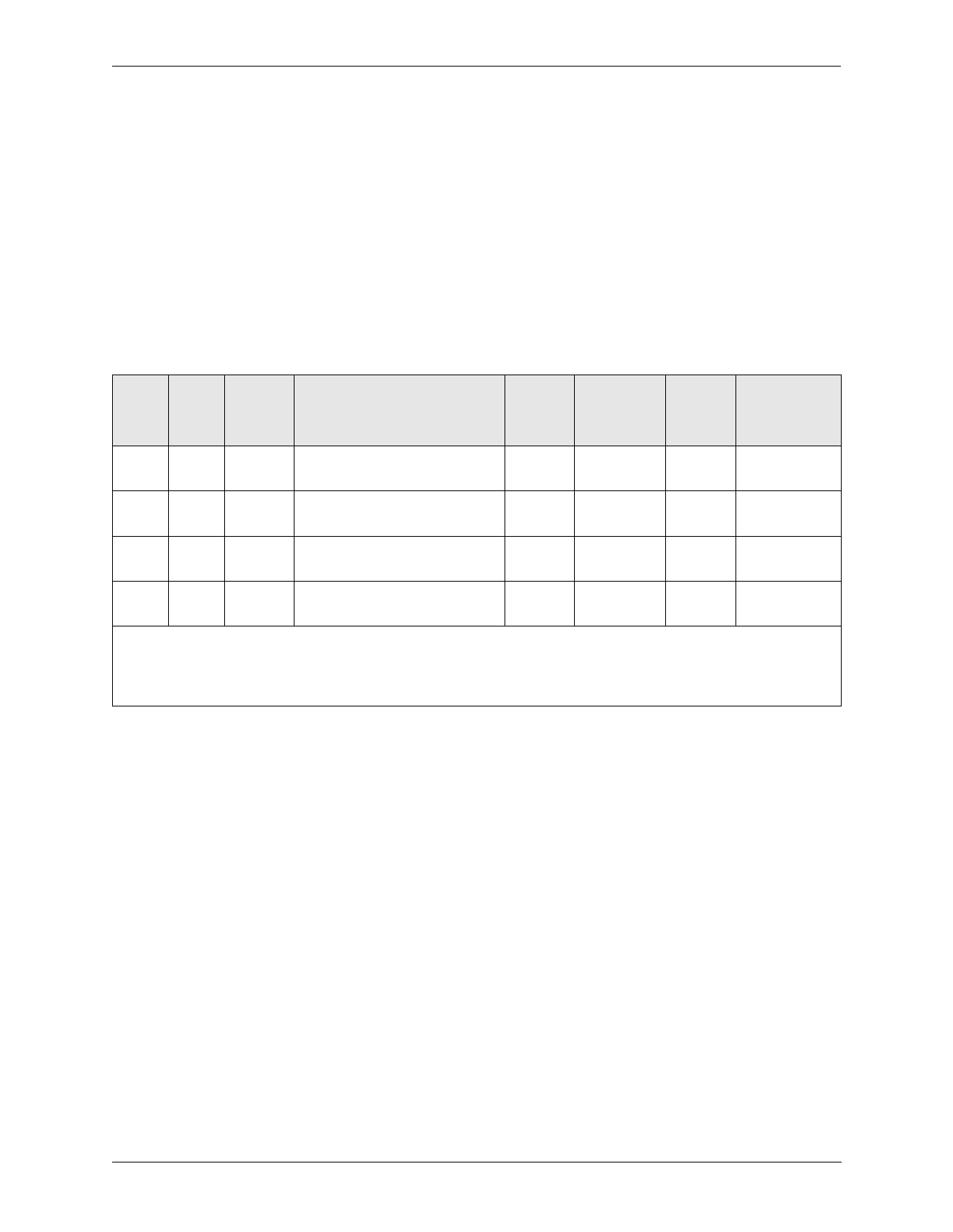

There are four configurations for the operational mode of the Bt8110/8110B (see

Table 1-1). These configurations are established by setting the three mode control

bits ([MODE[2:0]) and the enable framer bit [EN_FRMR] in the Mode Control

Register [mode; 0x40], in the microprocessor mode or on signal pins in the

hardware mode (AD[2:0] and CTRL[0]). Table 1-1 summarizes the

configurations and the input code applied to each.

Table 1-1. ADPCM Operational Modes

CTRL CTRL Mode

[1]

[0] Control

Function

Clock

Rate

(MHz)

Channel

Capacity

Clock

Rate

(MHz)

Channel

Capacity

x

0

100

Encoder/Decoder Interleaved(1)

6.144

24

8.192 32 Full-duplex

Full-duplex

x

0

101

Encoder Only

6.144

48

Half-duplex

8.192

64 Half-duplex

x

0

110

Decoder Only

6.144

48

Half-duplex

8.192

64 Half-duplex

0

1

100

Direct Framer Interface

12.352

24

Full-duplex

8.192

32 Full-duplex

NOTE(S):

(1) Interleaved operation means that the Bt8110/8110B alternates between encoder and decoder operation on consecutive

inputs. This requires that the inputs and outputs be interleaved (PCM/ADPCM/PCM, etc.) as well.

2. CTRL[1] and CTRL[0] are available only in the Bt8110B.

In T1 and E1 direct framer interface modes the Bt8110/8110B can connect

directly to a T1 or E1 framer providing 24 or 32 full-duplex channels of encoding.

These configurations are described in detail in Appendix B and C.

1.1.1 Signal Inputs and Outputs

The Bt8110/8110B provides both parallel and serial inputs and outputs. The 8-bit

parallel inputs are selected by setting the input PSIGEN high. The serial input is a

multiplexed encoder/decoder input to provide interleaved signals. The transfer

rate of the serial input and output is one-half the input clock rate (CLOCK). The

serial output is also multiplexed in interleaved encoder/decoder operation.

ADPCM inputs and outputs appear on the most significant bits.

The serial signal input and output words are 8 bits, with the most significant

bit (sign bit for PCM) appearing first. When transparent operation is selected for

a given channel for either an encoder or a decoder, all 8 bits are transferred

without modification from the input to both the serial and parallel outputs.

NOTE: The exception is with the Bt8110 when the parallel interface is selected in

the direct T1/E1 framer interface mode; then the decoder path PSIG[0]

must held at a logic low level.

1-2

Conexant

100060C