LT1210CT7TR Ver la hoja de datos (PDF) - Linear Technology

Número de pieza

componentes Descripción

Lista de partido

LT1210CT7TR Datasheet PDF : 16 Pages

| |||

LT1210

APPLICATI S I FOR ATIO

Power Supplies

The LT1210 will operate from single or split supplies from

±5V (10V total) to ±15V (30V total). It is not necessary to

use equal value split supplies, however the offset voltage

and inverting input bias current will change. The offset

voltage changes about 500µV per volt of supply mis-

match. The inverting bias current can change as much as

5µA per volt of supply mismatch, though typically the

change is less than 0.5µA per volt.

Power Supply Bypassing

To obtain the maximum output and the minimum distor-

tion from the LT1210, the power supply rails should be

well bypassed. For example, with the output stage pouring

1A current peaks into the load, a 1Ω power supply imped-

ance will cause a droop of 1V, reducing the available

output swing by that amount. Surface mount tantalum and

ceramic capacitors make excellent low ESR bypass ele-

ments when placed close to the chip. For frequencies

above 100kHz, use 1µF and 100nF ceramic capacitors.

If significant power must be delivered below 100kHz,

capacitive reactance becomes the limiting factor. Larger

ceramic or tantalum capacitors, such as 4.7µF, are recom-

mended in place of the 1µF unit mentioned above.

Inadequate bypassing is evidenced by reduced output

swing and “distorted” clipping effects when the output is

driven to the rails. If this is observed, check the supply pins

of the device for ripple directly related to the output

waveform. Significant supply modulation indicates poor

bypassing.

Thermal Considerations

The LT1210 contains a thermal shutdown feature which

protects against excessive internal (junction) tempera-

ture. If the junction temperature of the device exceeds the

protection threshold, the device will begin cycling be-

tween normal operation and an off state. The cycling is not

harmful to the part. The thermal cycling occurs at a slow

rate, typically 10ms to several seconds, which depends on

the power dissipation and the thermal time constants of

the package and heat sinking. Raising the ambient tem-

perature until the device begins thermal shutdown gives a

good indication of how much margin there is in the

thermal design.

For surface mount devices heat sinking is accomplished

by using the heat spreading capabilities of the PC board

and its copper traces. Experiments have shown that the

heat spreading copper layer does not need to be electri-

cally connected to the tab of the device. The PCB material

can be very effective at transmitting heat between the pad

area attached to the tab of the device, and a ground or

power plane layer either inside or on the opposite side of

the board. Although the actual thermal resistance of the

PCB material is high, the length/area ratio of the thermal

resistance between the layer is small. Copper board stiff-

eners and plated through holes can also be used to spread

the heat generated by the device.

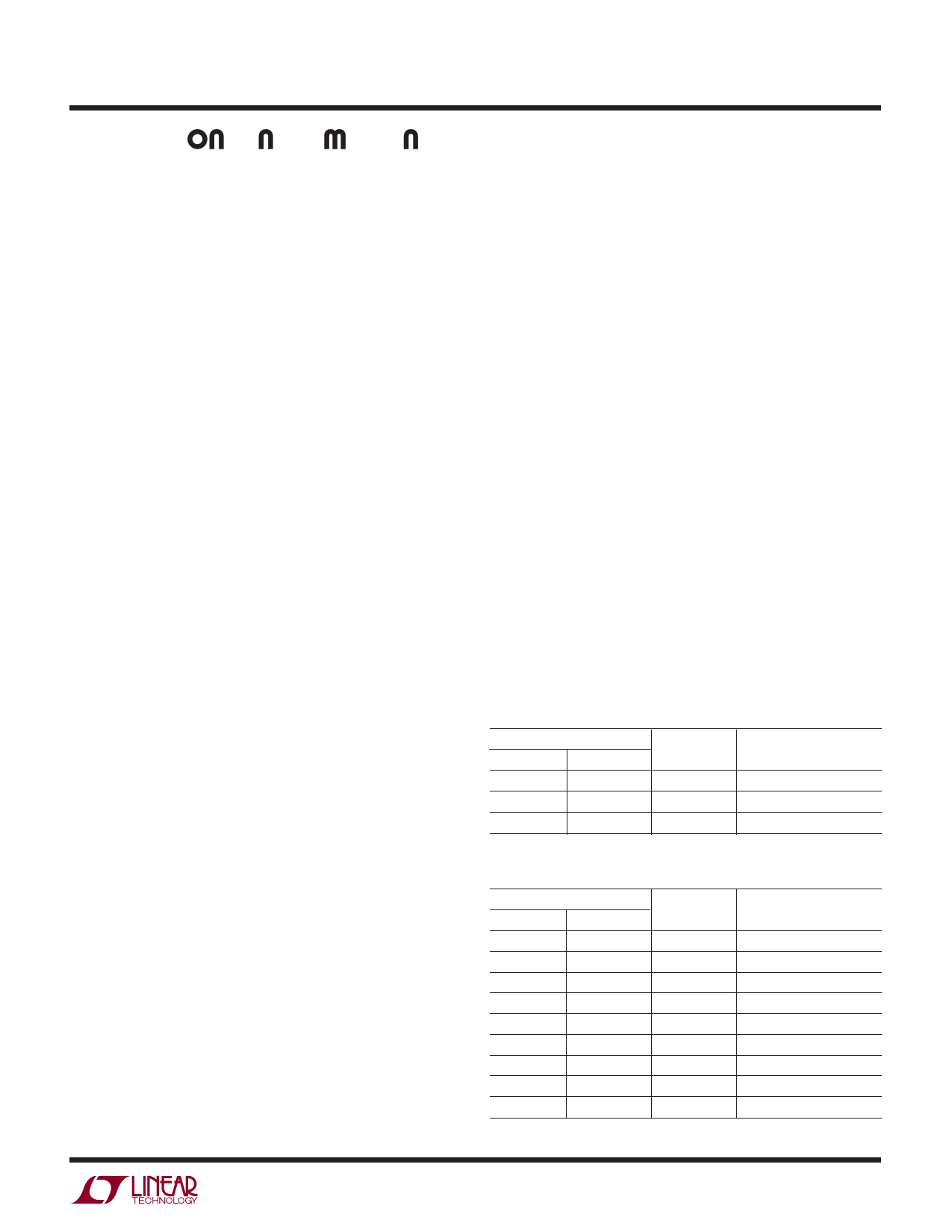

Tables 1 and 2 list thermal resistance for each package. For

the TO-220 package, thermal resistance is given for junc-

tion-to-case only since this package is usually mounted to

a heat sink. Measured values of thermal resistance for

several different board sizes and copper areas are listed for

each surface mount package. All measurements were

taken in still air on 3/32" FR-4 board with 2 oz copper. This

data can be used as a rough guideline in estimating

thermal resistance. The thermal resistance for each appli-

cation will be affected by thermal interactions with other

components as well as board size and shape.

Table 1. R Package, 7-Lead DD

COPPER AREA

THERMAL RESISTANCE

TOPSIDE* BACKSIDE BOARD AREA (JUNCTION-TO-AMBIENT)

2500 sq. mm 2500 sq. mm

1000 sq. mm 2500 sq. mm

125 sq. mm 2500 sq. mm

2500 sq. mm

2500 sq. mm

2500 sq. mm

25°C/W

27°C/W

35°C/W

*Tab of device attached to topside copper

Table 2. Fused 16-Lead SO Package

COPPER AREA

THERMAL RESISTANCE

TOPSIDE BACKSIDE BOARD AREA (JUNCTION-TO-AMBIENT)

2500 sq. mm 2500 sq. mm 5000 sq. mm

40°C/W

1000 sq. mm 2500 sq. mm 3500 sq. mm

46°C/W

600 sq. mm 2500 sq. mm 3100 sq. mm

48°C/W

180 sq. mm 2500 sq. mm 2680 sq. mm

49°C/W

180 sq. mm 1000 sq. mm 1180 sq. mm

56°C/W

180 sq. mm 600 sq. mm 780 sq. mm

58°C/W

180 sq. mm 300 sq. mm 480 sq. mm

59°C/W

180 sq. mm 100 sq. mm 280 sq. mm

60°C/W

180 sq. mm 0 sq. mm 180 sq. mm

61°C/W

1210fa

11