CS8416-CSZR Ver la hoja de datos (PDF) - Cirrus Logic

Número de pieza

componentes Descripción

Lista de partido

CS8416-CSZR Datasheet PDF : 60 Pages

| |||

CS8416

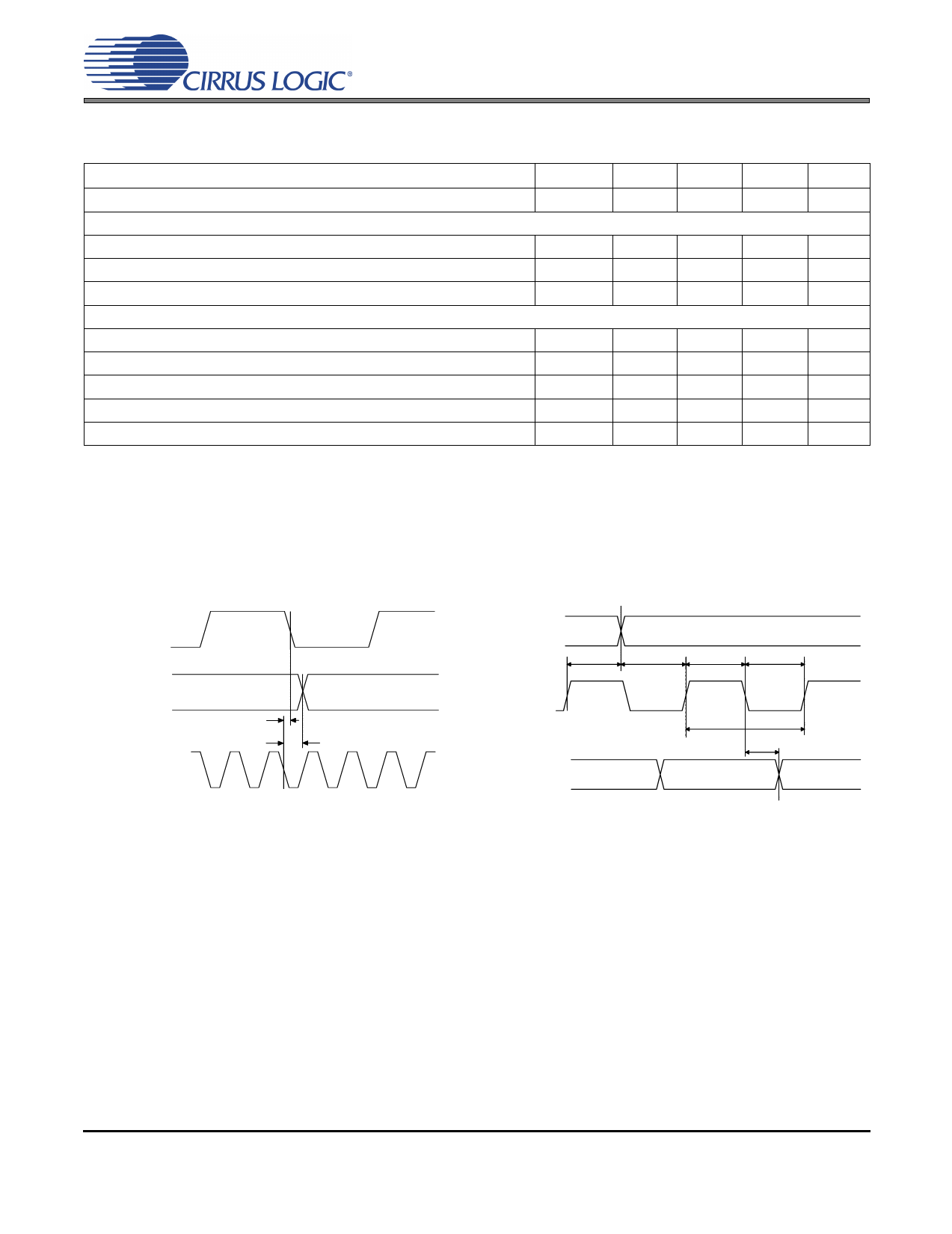

SWITCHING CHARACTERISTICS - SERIAL AUDIO PORTS

(Inputs: Logic 0 = 0 V, Logic 1 = VL; CL = 20 pF)

Parameter

Symbol Min Typ

OSCLK/OLRCK Active Edge to SDOUT Output Valid (Note 8) tdpd

-

-

Master Mode

RMCK to OSCLK active edge delay

RMCK to OLRCK delay

OSCLK and OLRCK Duty Cycle

Slave Mode

(Note 8) tsmd

0

-

(Note 9) tlmd

0

-

-

50

OSCLK Period

tsckw

36

-

OSCLK Input Low Width

tsckl

14

-

OSCLK Input High Width

tsckh

14

-

OSCLK Active Edge to OLRCK Edge

(Notes 8,9,10) tlrckd

10

-

OSCLK Edge Setup Before OSCLK Active-Edge (Notes 8,9,11) tlrcks

10

-

Max Units

23

ns

12

ns

12

ns

-

%

-

ns

-

ns

-

ns

-

ns

-

ns

Notes:

8. In Software Mode the active edges of OSCLK are programmable.

9. In Software Mode the polarity of OLRCK is programmable.

10. This delay is to prevent the previous OSCLK edge from being interpreted as the first one after OLRCK

has changed.

11. This setup time ensures that this OSCLK edge is interpreted as the first one after OLRCK has changed.

OSCLK

(output)

OLRCK

(output)

RMCK

(output)

t smd

t lm d

OLRCK

(input)

OSCLK

(input)

t lrckd

t lrcks

SDOUT

t sckh

tsckl

t sckw

tdpd

Figure 1. Audio Port Master Mode Timing

Figure 2. Audio Port Slave Mode and Data Input

DS578F3

9