HEF4731BD Ver la hoja de datos (PDF) - Philips Electronics

Número de pieza

componentes Descripción

Lista de partido

HEF4731BD Datasheet PDF : 4 Pages

| |||

Philips Semiconductors

Quadruple 64-bit static shift register

Product specification

HEF4731B; HEF4731V

LSI

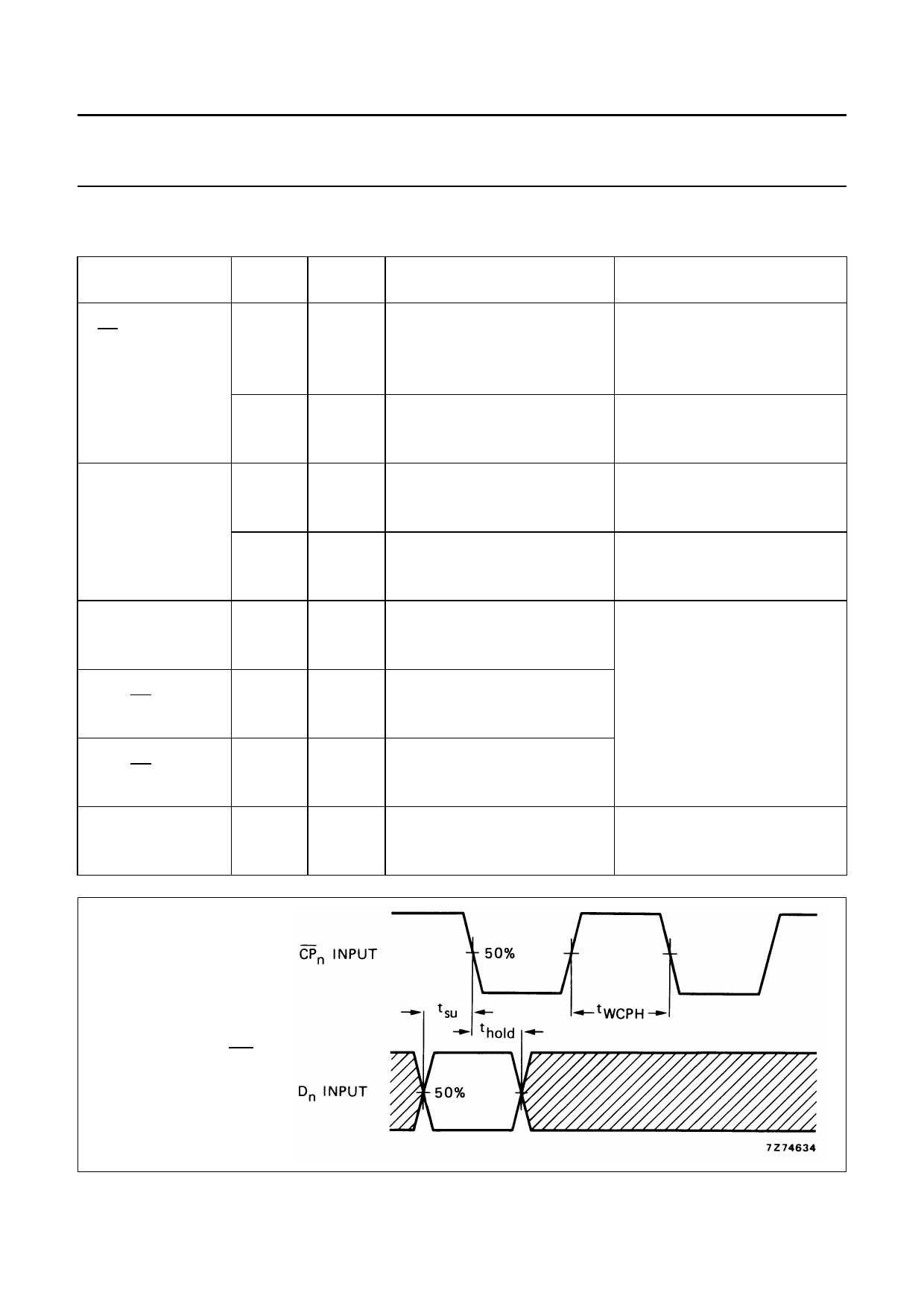

AC CHARACTERISTICS

VSS = 0 V; Tamb = 25 °C; CL = 50 pF; input transition times ≤ 20 ns

VDD

V

SYMBOL MIN. TYP. MAX.

Propagation delays

CP → O63

HIGH to LOW

LOW to HIGH

Transition times O63

HIGH to LOW

LOW to HIGH

Minimum clock

pulse width; HIGH

Set-up time

D → CP

Hold time

D → CP

Maximum clock

pulse frequency

5

10 tPHL

15

5

10 tPLH

15

5

10 tTHL

15

5

10 tTLH

15

5

10 tWCPH

15

5

10 tsu

15

5

10 thold

15

5

10 fmax

15

115 230 ns

55 110 ns

40

80 ns

130 260 ns

65 130 ns

45

90 ns

30

60 ns

12

24 ns

10

20 ns

40

80 ns

20

40 ns

15

30 ns

200

80

ns

75

30

ns

50

20

ns

25

−5

ns

15

−5

ns

15

−5

ns

50

20

ns

30

10

ns

20

5

ns

2.25

6

MHz

6

16

MHz

9

25

MHz

TYPICAL EXTRAPOLATION

FORMULA

132 ns + (0,26 ns/pF) CL

47 ns + (0,16 ns/pF) CL

34 ns + (0,11 ns/pF) CL

138 ns + (0,45 ns/pF) CL

56 ns + (0,19 ns/pF) CL

39 ns + (0,13 ns/pF) CL

10 ns + (0,40 ns/pF) CL

3 ns + (0,18 ns/pF) CL

3 ns + (0,13 ns/pF) CL

8 ns + (0,65 ns/pF) CL

5 ns + (0,30 ns/pF) CL

5 ns + (0,20 ns/pF) CL

see also waveforms Fig.4

Note: the maximum

power dissipation has

to be observed

Fig.4

Waveforms showing

minimum clock pulse

width, set-up and hold

times for D to CP.

Set-up and hold times

are shown as positive

values but may be

specified as negative

values.

January 1995

4