AV9248F-61 Ver la hoja de datos (PDF) - Integrated Circuit Systems

Número de pieza

componentes Descripción

Lista de partido

AV9248F-61 Datasheet PDF : 9 Pages

| |||

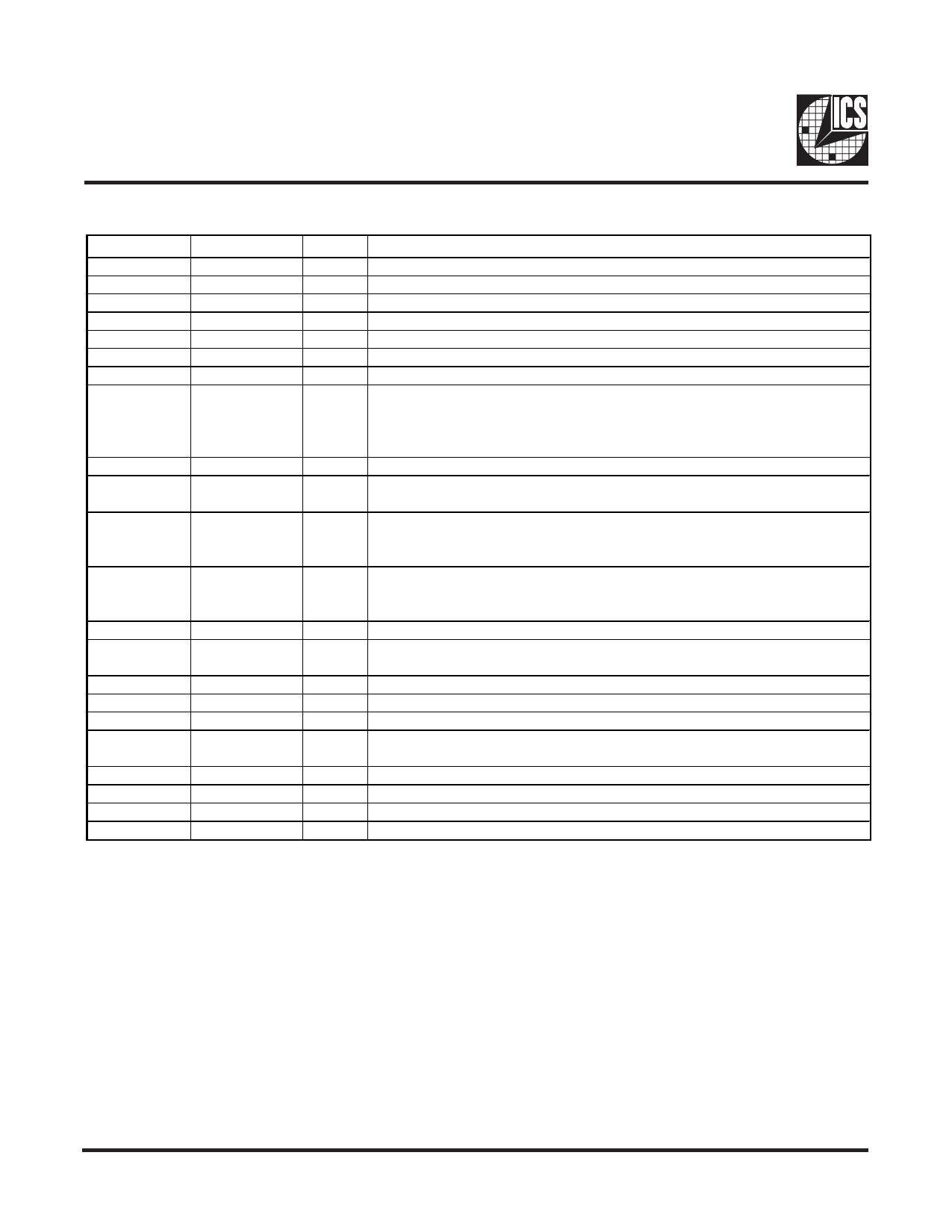

ICS9248-61

Pin Descriptions

Pin number

2

3

4

7

8

12

13

14

15

16

17

18

19

20

21

22

25

26

28

1,27

23,24

5,6,9,10, 11

Pin name

X1

X2

PCICLK_F

GNDPCI

VDDPCI

PCICLK_E

VDD48

SEL 100_66#/

48MHz

GND48

DIV4#

PD#

CPU_STOP#

VDDCOR

PCI-STOP#

GNDR/C

GNDLCPU

VDDLCPU

SPREAD#

VDDR

REF(0:1)

CPUCLK (0:1)

PCICLK (1:4)

Type

Input

Output

Output

Power

Power

Output

Power

Input

Power

Input

Input

Input

Input

Input

Input

Power

Power

Output

Input

Output

0utput

Output

Description

14.318 MHz crystal input

14.318 MHz crystal output

3.3 V free running PCI clock output, will not be stopped by the PCI_STOP#

Ground for PCI clock outputs

3.3 V power for the PCI clock outputs

Early PCICLK output, offset from other PCICLKs, stopped by PCI-STOP#

3.3 V power for 48 MHz clocks

on power-on control for the frequency of clocks at the CPU & PCICLK output pins. If

logic "0" is used the 66.6 MHz frequency is selected. If Logic "1" is used, the 100

MHz frequency is selected. The PCI clock is multiplexed to run at 33.3 MHz for both

selects

Ground for 48 MHz clocks

Active low input, enables the CPUCLK and the PCICLK to run at 1/4 of the regular

frequecies

Asynchronous active low input pin used to power down the device into a low power

state. The internal clocks are disabled and the VCO and the crystal are stopped. The

latency of the power down will not be greater than 3ms.

Asynchronous active low input pin used to stop the CPUCLK in active low state, all

other clocks will continue to run. The CPUCLK will have a "Turnon " latency of at

least 3 CPU clocks.

3.3 V power for the core

Synchronous active low input used to stop the PCICLK in active low state. It will not

effect PCICLK_F or any other outputs.

Ground for REFCLK, Crystal & Core

Ground for the CPU and Host clock outputs

2.5 V power for the CPU and Host clock outputs

power-on spread spectrum enable option. Active low = spread spectrum clocking

enable. Active high = spread spectrum clocking disable.

3.3 V power for the REFCLK and crystal clock outputs

3.3V, 14.318 MHz reference clock output.

2.5 V CPU and Host clock outputs

3.3 V PCI clock outputs, generating timing requirements

2