ICS9248-95 Ver la hoja de datos (PDF) - Integrated Circuit Systems

Número de pieza

componentes Descripción

Lista de partido

ICS9248-95 Datasheet PDF : 16 Pages

| |||

ICS9248 - 95

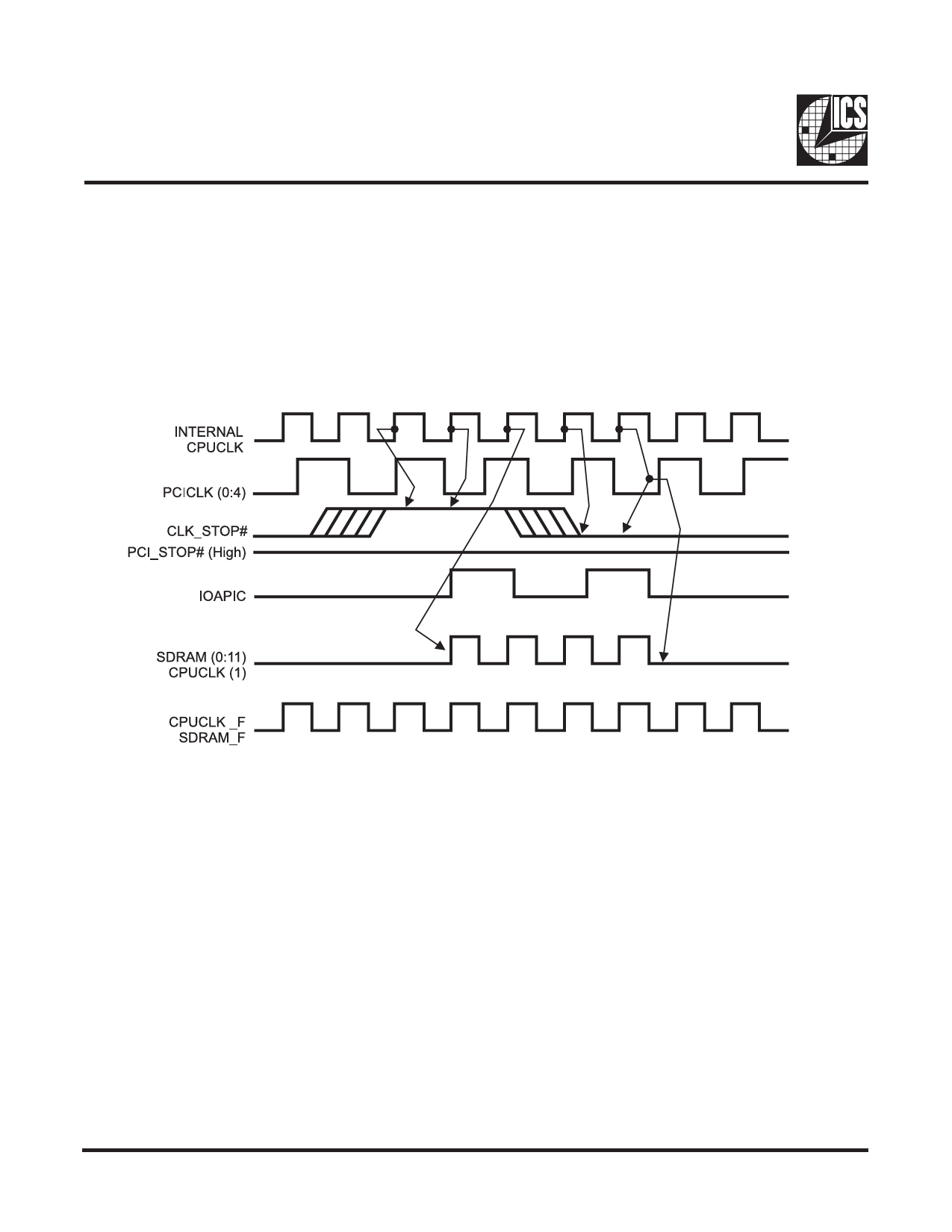

CLK_STOP# Timing Diagram

CLK_STOP# is an asychronous input to the clock synthesizer. It is used to turn off the CPU clocks for low power operation.

CLK_STOP# is synchronized by the ICS9248-95. The minimum that the CPU clock is enabled (CPU_STOP# high pulse) is 100

CPU clocks. All other clocks will continue to run while the CPU clocks are disabled. The CPU clocks will always be stopped in

a low state and start in such a manner that guarantees the high pulse width is a full pulse. CPU clock on latency is less than 4

CPU clocks and CPU clock off latency is less than 4 CPU clocks.

Notes:

1. All timing is referenced to the internal CPU clock.

2. CLK_STOP# is an asynchronous input and metastable conditions may exist. This signal is synchronized

to the CPU clocks inside the ICS9248-95.

3. IOAPIC output is Stopped Glitch Free by CPUSTOP# going low.

4. SDRAM-F output is controlled by Buffer in signal, not affected by the ICS9248-95

CLK_STOP# signal. SDRAM (0:11) are controlled as shown.

5. All other clocks continue to run undisturbed.

310D—04/12/05

8