IDT7028L15PFI Ver la hoja de datos (PDF) - Integrated Device Technology

Número de pieza

componentes Descripción

Lista de partido

IDT7028L15PFI Datasheet PDF : 17 Pages

| |||

IDT7028L

High-Speed 64K x 16 Dual-Port Static RAM

Industrial and Commercial Temperature Ranges

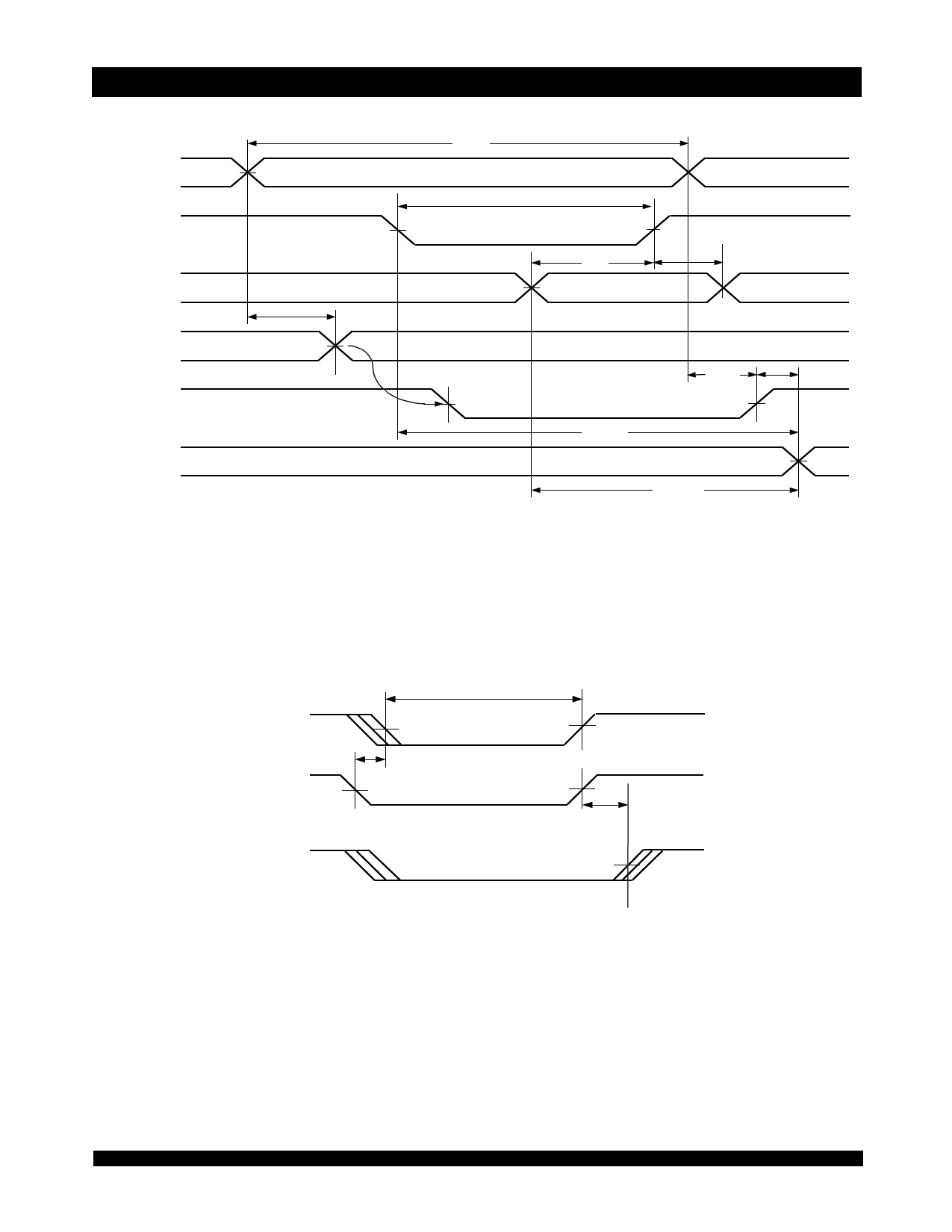

Timing Waveform of Write with Port-to-Port Read and BUSY(M/S = VIH)(2,4,5)

tWC

ADDR"A"

MATCH

tWP

R/W"A"

DATAIN "A"

tAPS (1)

tDW

tDH

VALID

ADDR"B"

MATCH

BUSY"B"

tBAA

tBDA

tBDD

DATAOUT "B"

tWDD

tDDD (3)

NOTES:

1. To ensure that the earlier of the two ports wins. tAPS is ignored for M/S = VIL (SLAVE).

2. CEL = CER = VIL, refer to Chip Enable Truth Table.

3. OE = VIL for the reading port.

4. If M/S = VIL (SLAVE), BUSY is an input. Then for this example BUSY"A" = VIH and BUSY"B" input is shown above.

5. All timing is the same for left and right ports. Port "A" may be either the left or right port. Port "B" is the port opposite from port "A".

VALID

4836 drw 11

Timing Waveform of Write with BUSY (M/S = VIL)

tWP

R/W"A"

BUSY"B"

tWB(3)

tWH (1)

R/W"B"

(2)

NOTES:

1. tWH must be met for both BUSY input (SLAVE) and output (MASTER).

2. BUSY is asserted on port "B" blocking R/W"B", until BUSY"B" goes HIGH.

3. tWB is only for the 'Slave' version.

.

4836 drw 12

61.412