LAN91C111I-NU Ver la hoja de datos (PDF) - SMSC -> Microchip

Número de pieza

componentes Descripción

Lista de partido

LAN91C111I-NU Datasheet PDF : 128 Pages

| |||

10/100 Non-PCI Ethernet Single Chip MAC + PHY

Datasheet

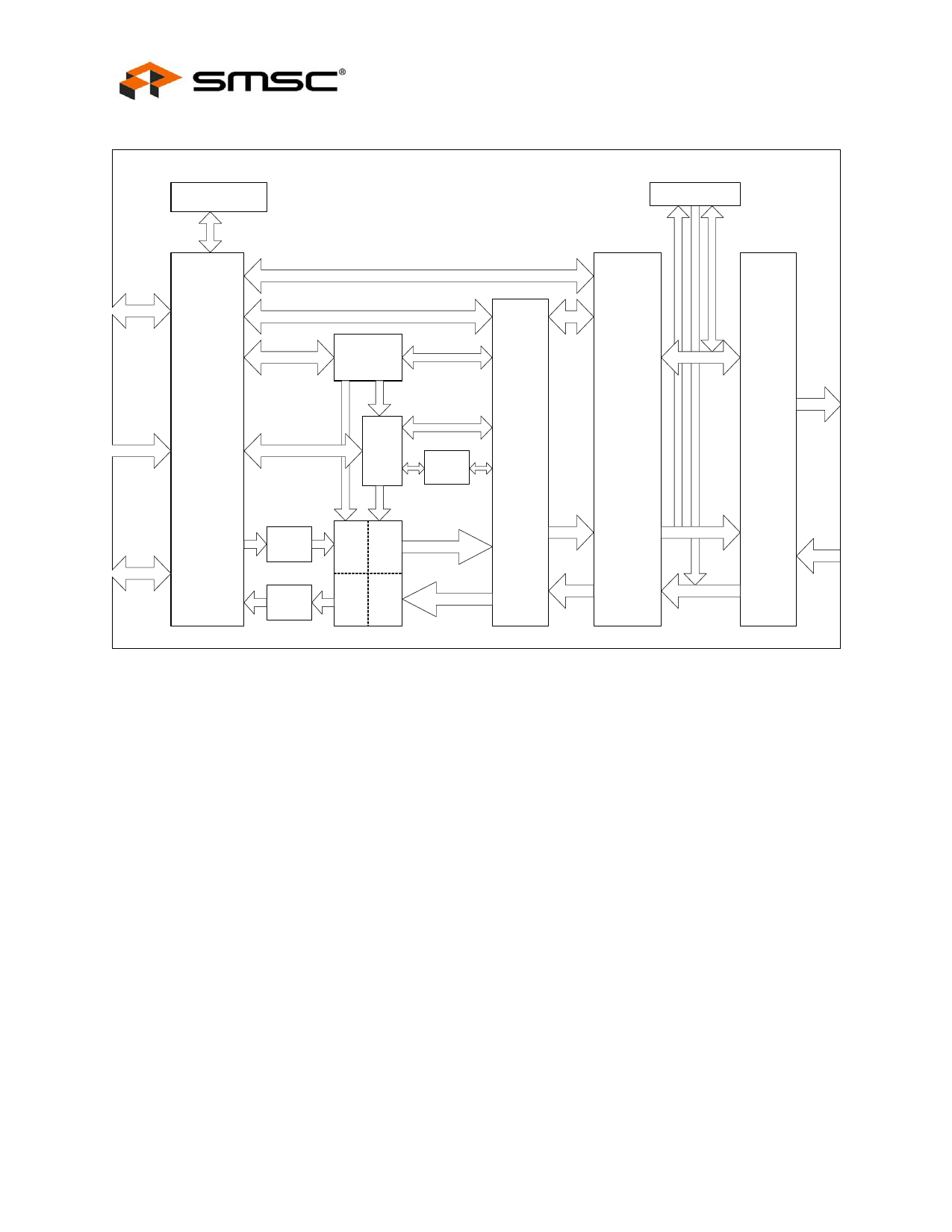

EEPROM

INTERFACE

MII

Control

Address

8-32 bit

Bus

Interface

Unit

Control

Control

Control

Arbiter

Control

MMU

TX/RX

FIFO

Pointer

Control

Control

DMA

Ethernet

Protocol

Handler

(EPH)

TPO

10/100

PHY

Data

WR

FIFO

RD

FIFO

8K Byte

Dynamically

Allocated

SRAM

32-bit Data

32-bit Data

TX Data

RX Data

TXD[0-3]

TPI

RXD[0-3]

Figure 3.2 Block Diagram

The diagram shown in Figure 3.2 describes the supported Host interfaces, which include ISA or

Generic Embedded. The Host interface is an 8, 16 or 32 bit wide address / data bus with extensions

for 32, 16 and 8 bit embedded RISC and ARM processors.

The figure shown next page describes the SMSC LAN91C111 functional blocks required to integrate

a 10/100 Ethernet Physical layer framer to the internal MAC.

Revision 1.91 (08-18-08)

12

DATASHEET

SMSC LAN91C111 REV C