IS62C1024L-35Q Ver la hoja de datos (PDF) - Integrated Circuit Solution Inc

Número de pieza

componentes Descripción

Lista de partido

IS62C1024L-35Q Datasheet PDF : 8 Pages

| |||

IS62C1024L

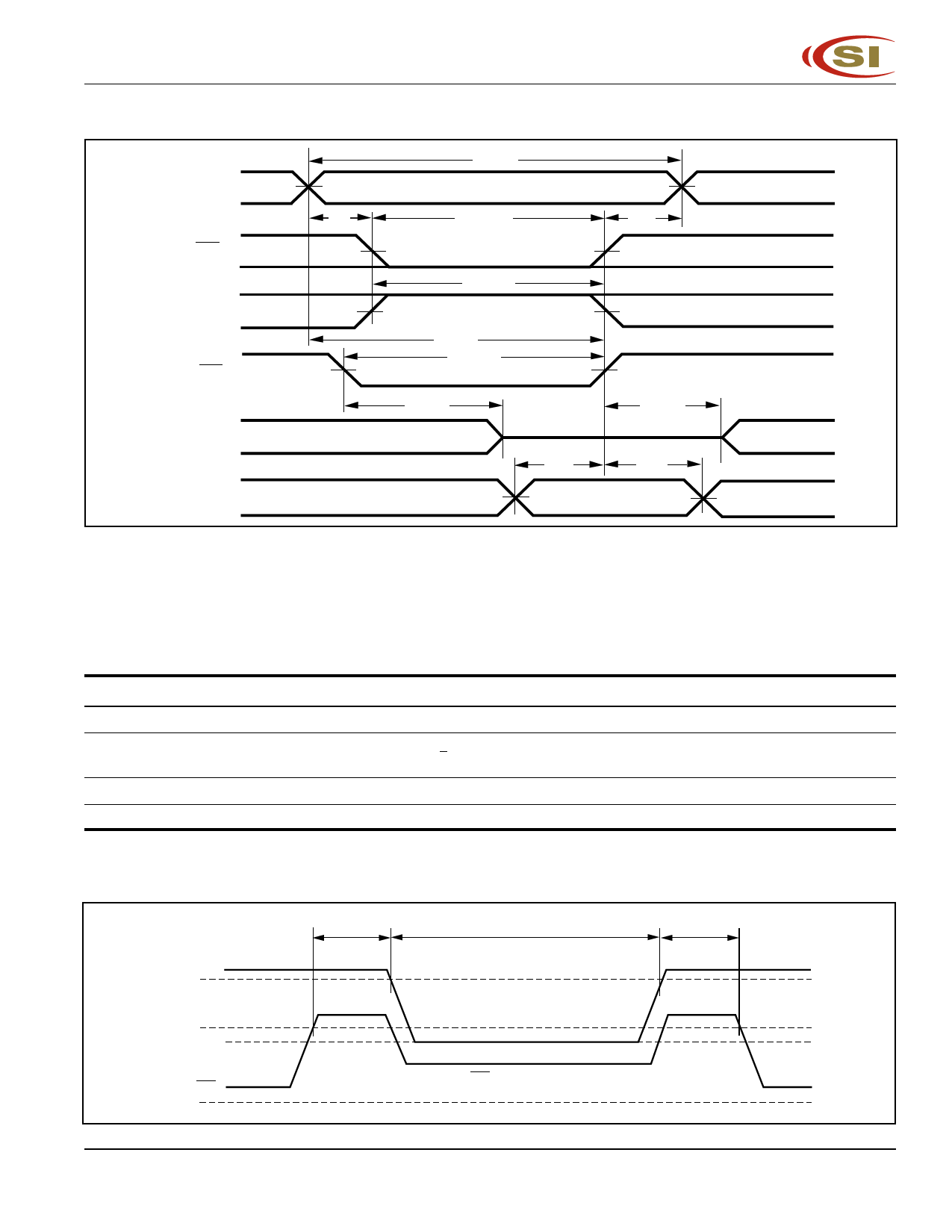

WRITE CYCLE NO. 2 (+- , CE2 Controlled)(1,2)

tWC

ADDRESS

tSA

tSCE1

tHA

CE1

CE2

WE

DOUT

DIN

tSCE2

tAW

tPWE(4)

tHZWE

DATA UNDEFINED

HIGH-Z

tLZWE

tSD

tHD

DATA-IN VALID

Notes:

1. The internal write time is defined by the overlap of CE1 LOW, CE2 HIGH and WE LOW. All signals must be in valid states to

initiate a Write, but any one can go inactive to terminate the Write. The Data Input Setup and Hold timing are referenced to the

rising or falling edge of the signal that terminates the Write.

2. I/O will assume the High-Z state if OE = VIH.

DATA RETENTION SWITCHING CHARACTERISTICS

Symbol

VDR

IDR

Parameter

Vcc for Data Retention

Data Retention Current

Test Condition

See Data Retention Waveform

Vcc = 3.0V, CE1 > Vcc 0.2V

tSDR

Data Retention Setup Time See Data Retention Waveform

tRDR

Recovery Time

See Data Retention Waveform

Min. Max. Unit

2.0 5.5

V

Com. 250

µA

Ind. 400

0

ns

tRC

ns

DATA RETENTION WAVEFORM (+- Controlled)

VCC

5.0V

tSDR

Data Retention Mode

tRDR

3.0V

VDR

CE1

GND

CE1 ≥ VCC - 0.2V

Integrated Circuit Solution Inc.

7

SR017-0C