MIC1832(Old_V) Ver la hoja de datos (PDF) - Micrel

Número de pieza

componentes Descripción

Lista de partido

MIC1832 Datasheet PDF : 8 Pages

| |||

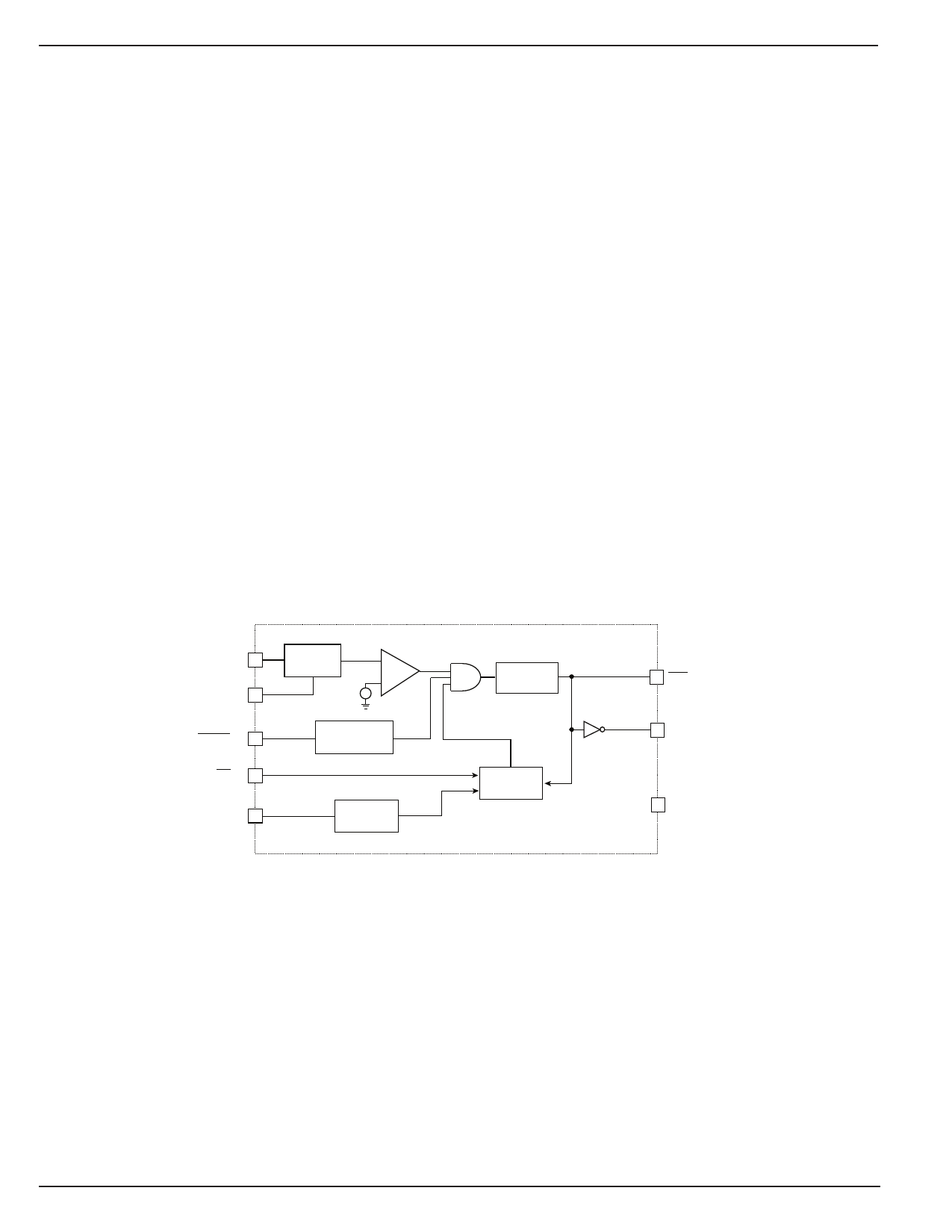

MIC1832 µP Supervisory Circuit

Circuit Description

Power Monitor

The RST and RST pins are asserted whenever VCC

falls below the reset threshold voltage as determined by

the TOL pin. A 5% tolerance level (2.88V reset

threshold voltage) can be selected by connecting the

TOL pin to ground and a 10% tolerance (2.55V reset

threshold voltage) can be selected by connecting the

TOL pin to VCC. The reset pins will remain asserted for

a period of 250ms after VCC has risen above the reset

threshold voltage. The reset function ensures the

microprocessor is properly reset and powers up into a

known condition after a power failure. RST will remain

valid with VCC as low as 1.4V.

8++62

8++

456

J42,

456

8++62

J427

Figure 1. Power-Up/Power-Down Sequence

J56

56

J6,

Note:

The maximum time between high-to-low transitions (tTD) on the

watchdog input (ST) is determined by the voltage applied to the

TD pin. If the watchdog input sees a high-to-low transition prior to

the timeout period, the watchdog timer will be reset.

Figure 2. Watchdog Input

Watchdog Timer

The microprocessor can be monitored by connecting

the ST pin (watchdog input) to a bus line or I/O line. If a

high-to-low transition doesn’t occur on the ST pin within

the watchdog timeout period (determined by TD pin, see

Table 1), the RST and RST pins will be asserted

resulting in a microprocessor reset. RST and RST will

remain asserted for at least 250ms when this occurs. A

minimum pulse of 75ns or any transition high-to-low on

the ST pin will reset the watchdog timer. The watchdog

timer will be reset if ST sees a valid transition within the

watchdog timeout period.

tPB

Pushbutton Reset Input

tPDLY

The PBRST input can be driven with a manual

PBRST

pushbutton switch or with external logic signals. The

tRST

input is internally debounced and requires an active low

signal to force the reset outputs into their active states.

RST

The PBRST input will recognize any pulse that is 20ms

in duration or greater and will ignore all pulses that are

RST

less than 1ms in duration.

Figure 3. Pushbutton Reset

6