LT1671CMS8 Ver la hoja de datos (PDF) - Linear Technology

Número de pieza

componentes Descripción

Lista de partido

LT1671CMS8 Datasheet PDF : 12 Pages

| |||

LT1671

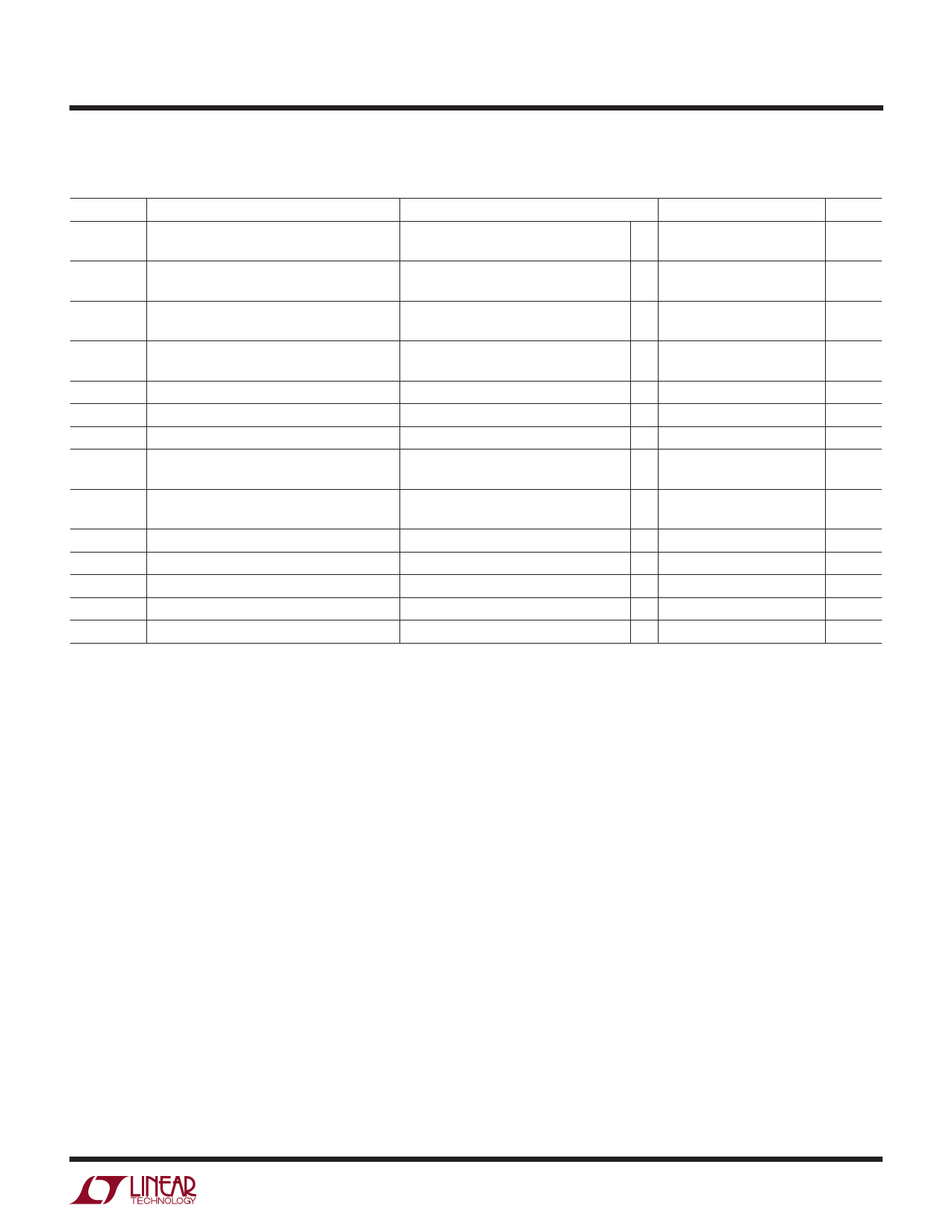

ELECTRICAL CHARACTERISTICS

The q denotes specifications which apply over the full operating temperature range, otherwise specifications are TA = 25°C.

V+ = 5V, V– = – 5V, VOUT(Q) = 1.4V, VLATCH = VCM = 0V unless otherwise noted.

SYMBOL

VOH

VOL

I+

I–

PARAMETER

Output Voltage Swing High

Output Voltage Swing Low

Positive Supply Current

Negative Supply Current

CONDITIONS

V + ≥ 4.6V, IOUT = 400µA

V + ≥ 4.6V, IOUT = 4mA

IOUT = – 400µA

IOUT = – 4mA

MIN

q 2.7

q 2.4

q

q

q

TYP MAX

3.1

3.0

0.3

0.5

0.4

450 800

1000

75

200

250

UNITS

V

V

V

V

µA

µA

µA

µA

VIH

LATCH Pin High Input Voltage

VIL

LATCH Pin Low Input Voltage

IIL

LATCH Pin Current

t PD1

Propagation Delay

VLATCH = 0V

∆VIN = 100mV, VOD = 20mV

q

2

V

q

0.8

V

q – 1000 – 250

nA

60

80

ns

q

110

ns

t PD2

Propagation Delay (Note 7)

∆VIN = 100mV, VOD = 5mV

85

100

ns

q

130

ns

∆t PD

t LPD

t SU

tH

t PW(D)

Differential Propagation Delay (Note 7)

Latch Propagation Delay (Note 8)

Latch Setup Time (Note 8)

Latch Hold Time (Note 8)

Minimum Disable Pulse Width

∆VIN = 100mV, VOD = 5mV

15

30

ns

60

ns

– 15

ns

35

ns

30

ns

Note 1: Absolute Maximum Ratings are those values beyond which the life

of a device may be impaired.

Note 2: This parameter is guaranteed to meet specified performance

through design and characterization. It has not been tested.

Note 3: The LT1671CS8 and LT1671CMS8 are guaranteed to meet

specified performance from 0°C to 70°C and are designed, characterized

and expected to meet these extended temperature limits, but are not tested

at – 40°C and 85°C. The LT1671IS8 is guaranteed to meet the extended

temperature limits.

Note 4: Input offset voltage (VOS) is defined as the average of the two

voltages measured by forcing first one output, then the other to 1.4V.

Note 5: Input bias current (IB) is defined as the average of the two input

currents.

Note 6: Input voltage range is guaranteed in part by CMRR testing and in

part by design and characterization.

Note 7: tPD and ∆tPD cannot be measured in automatic handling

equipment with low values of overdrive. The LT1671 is 100% tested with a

100mV step and 20mV overdrive. Correlation tests have shown that tPD

and ∆tPD limits can be guaranteed with this test, if additional DC tests are

performed to guarantee that all internal bias conditions are correct.

Propagation delay (tPD) is measured with the overdrive added to the actual

VOS. Differential propagation delay is defined as:

∆tPD = tPDLH – tPDHL

Note 8: Latch propagation delay (tLPD) is the delay time for the output to

respond when the LATCH pin is deasserted. Latch setup time (tSU) is the

interval in which the input signal must remain stable prior to asserting the

latch signal. Latch hold time (tH) is the interval after the latch is asserted in

which the input signal must remain stable.

3