MT9126AE Ver la hoja de datos (PDF) - Mitel Networks

Número de pieza

componentes Descripción

Lista de partido

MT9126AE Datasheet PDF : 22 Pages

| |||

MT9126

Preliminary Information

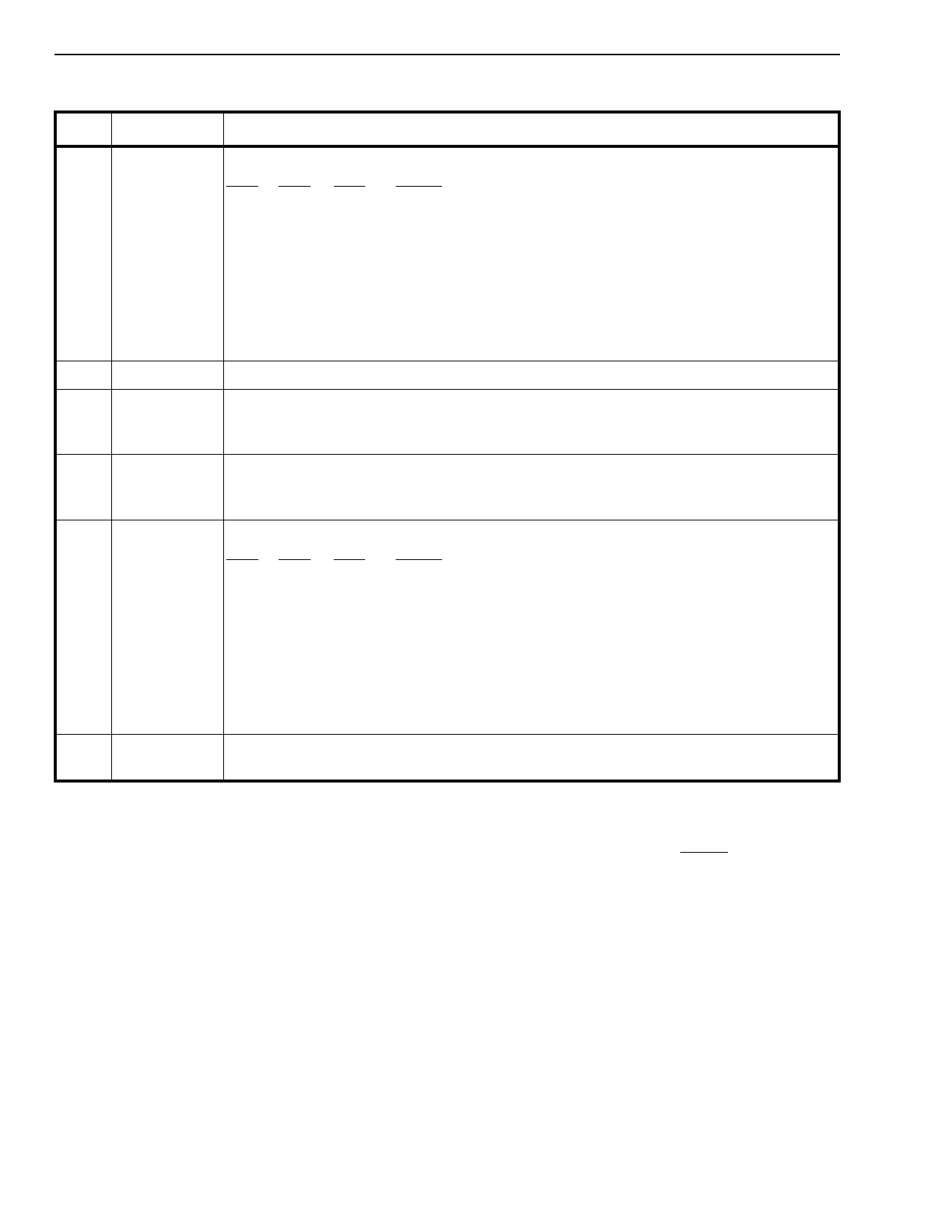

Pin Description

Pin #

19

20

21

22

23

24

25

26

27

28

Name

MS1

MS2

MS3

VDD

ADPCMi

ADPCMo

MS4

MS5

MS6

EN2

Description

Mode Selects 1, 2 and 3 (Inputs). Mode selects for all four encoders.

MS3 MS2 MS1 MODE

0

0

0

32 kbit/s ADPCM

0

0

1

24 kbit/s ADPCM

0

1

0

16 kbit/s ADPCM in EN1/ENB1 when SEL=0

in EN2/ENB2 when SEL=1

0

1

1

ADPCM Bypass for 32 kbit/s and 24 kbit/s

1

0

0

ADPCM Bypass for 16 kbit/s

1

0

1

PCM Bypass (64 kbit/s) to PCM1 if SEL=0, PCM2 if SEL=1

1

1

0

Algorithm reset (ITU-T optional reset)

1

1

1

ADPCMo disable

Positive Power Supply. Nominally 5 volts +/-10%

Serial ADPCM Stream ( Input). 128 kbit/s to 4096 kbit/s serial ADPCM word input

stream. Data bits are clocked in on falling edge of BCLK in SSI mode and clocked in on

the 3/4 bit edge of MCLK in ST-BUS mode.

Serial ADPCM Stream (Output). 128 kbit/s to 4096 kbit/s serial ADPCM word output

stream. Data bits are clocked out by rising edge of BCLK in SSI mode and clocked out by

MCLK divided by two in ST-BUS mode.

Mode Selects 4, 5 and 6 (Inputs). Mode selects for all four decoders.

MS6 MS5 MS4 MODE

0

0

0

32 kbit/s ADPCM

0

0

1

24 kbit/s ADPCM

0

1

0

16 kbit/s ADPCM in EN1/ENB1 when SEL=0

in EN2/ENB2 when SEL=1

0

1

1

ADPCM Bypass for 32 kbit/s and 24 kbit/s

1

0

0

ADPCM Bypass for 16 kbit/s

1

0

1

PCM Bypass (64 kbit/s) to PCM1 if SEL=0, PCM2 if SEL=1

1

1

0

Algorithm reset (ITU-T optional reset)

1

1

1

PCMo1/2 disable

Enable Strobe 2 (Output). This 8 bit wide, active high strobe is active during the B2

PCM channel in ST-BUS mode. Forced to high impedance when LINEAR=1.

Notes:

All unused inputs should be connected to logic low or high unless otherwise stated. All outputs should be left open circuit when not used.

All inputs have TTL compatible logic levels except for MCLK which has CMOS compatible logic levels and PWRDN which has Schmitt

trigger compatible logic levels.

All outputs are CMOS with CMOS logic levels (See DC Electrical Characteristics).

8-36