PCD5003 Ver la hoja de datos (PDF) - Philips Electronics

Número de pieza

componentes Descripción

Lista de partido

PCD5003 Datasheet PDF : 44 Pages

| |||

Philips Semiconductors

Advanced POCSAG Paging Decoder

Product specification

PCD5003

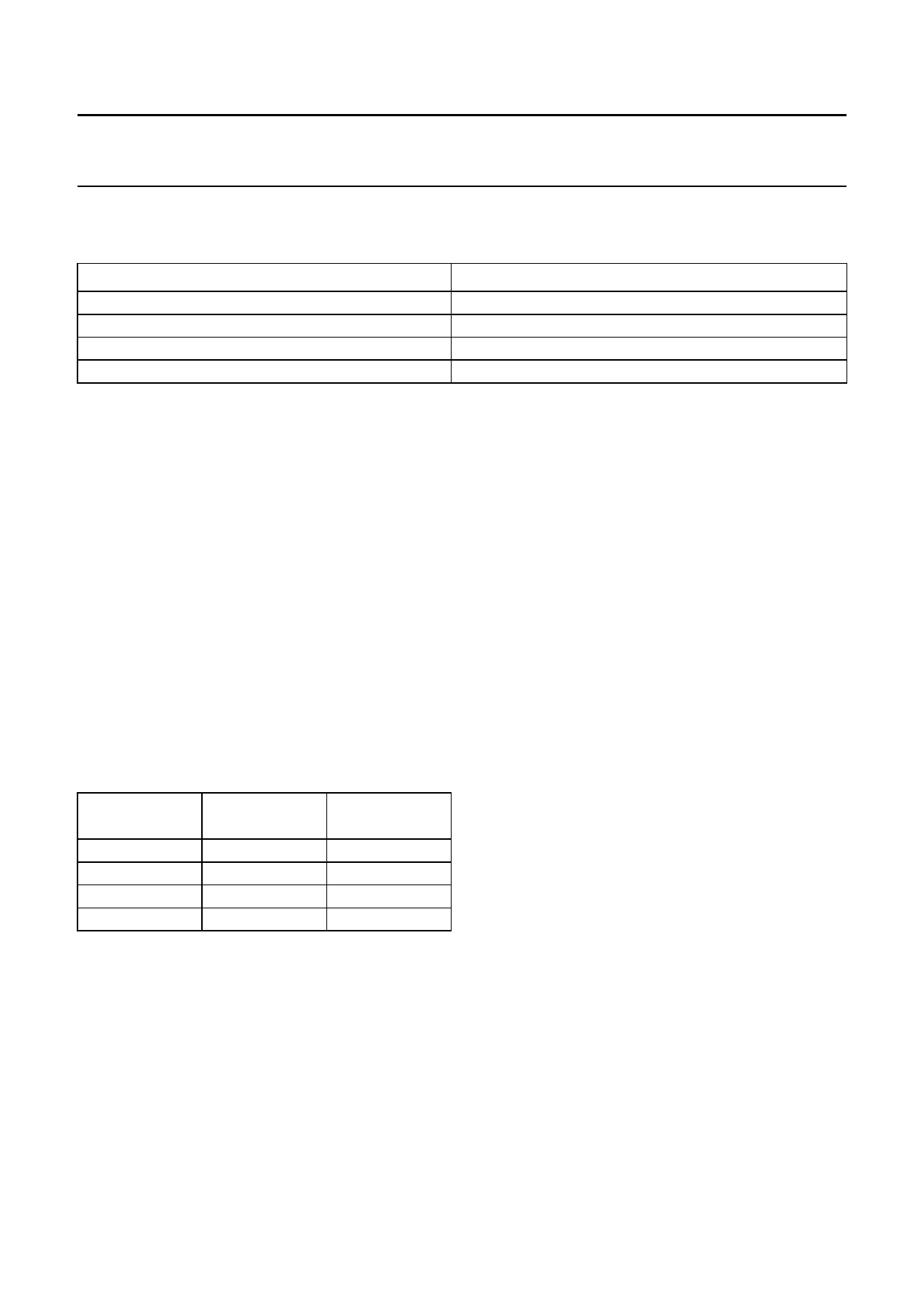

7.3 Error correction

Table 2 Error correction

ITEM

Preamble

Synchronization codeword

Address codeword

Message codeword

DESCRIPTION

4 random errors in 31 bits

2 random errors in 32 bits

2 random errors, plus: 4-bit burst errors (optional)

2 random errors, plus: 4-bit burst errors (optional)

In the PCD5003 error correction methods have been

implemented as shown in Table 2.

Random error correction is default for both address and

message codewords. In addition, burst error correction

can be enabled by SPF programming. Up to 3 erroneous

bits in a 4-bit burst can be corrected.

The error type detected for each codeword is identified in

the message data output to the microcontroller, allowing

rejection of calls with too many errors.

7.6 OFF status

In OFF status the decoder will neither activate the receiver

or oscillator enable outputs, nor process any data at the

data input. The crystal oscillator remains active to permit

communication with the microcontroller.

In both operating states an accurate timing reference is

available via the REF output. By SPF programming the

signal periodicity may be selected as 32.768 kHz, 50 Hz,

2 Hz or 1⁄60 Hz.

7.4 Operating states

The PCD5003 has 2 operating states:

• ON status

• OFF status.

The operating state is determined by a Direct Control input

(DON) and bit D4 in the control register (see Table 3).

Table 3 Truth table for decoder operating status

DON INPUT

0

0

1

1

CONTROL BIT

D4

0

1

0

1

OPERATING

STATUS

OFF

ON

ON

ON

7.5 ON status

In ON status the decoder pulses the receiver and oscillator

enable outputs (respectively RXE and ROE) according to

the code structure and the synchronization algorithm. Data

received serially at the data input (RDI) is processed for

call receipt. Reception of a valid paging call is signalled to

the microcontroller by means of an interrupt signal.

The received address and message data can then be read

via the I2C-bus interface.

7.7 Reset

The decoder can be reset by applying a positive pulse on

input pin RST. A power-on reset circuit consisting of an RC

network can be connected to this input as well. Conditions

during and after a reset are described in Chapter

“Operating instructions”.

For successful reset at power-on, a HIGH level must be

present on the RST pin while the device is powering-up.

This can be applied by the microcontroller, or via a suitable

RC power-on reset circuit connected to the RST input.

Reset circuit details and conditions during and after a reset

are described in Chapter 8

7.8 Bit rates

The PCD5003 can be configured for data rates of 512,

1200 or 2400 bit/s by SPF programming. These data

rates are derived from a single 76.8 kHz oscillator

frequency.

7.9 Oscillator

The oscillator circuit is designed to operate at 76.8 kHz.

Typically, a tuning fork crystal will be used as a frequency

source. Alternatively, an external clock signal can be

applied to pin XTAL1 (amplitude = VDD to VSS), but a

slightly higher oscillator current is consumed. A 2.2 MΩ

feedback resistor connected between XTAL1 and XTAL2

is required for proper operation.

1997 Jun 24

8