4246 Ver la hoja de datos (PDF) - Peregrine Semiconductor Corp.

Número de pieza

componentes Descripción

Lista de partido

4246 Datasheet PDF : 8 Pages

| |||

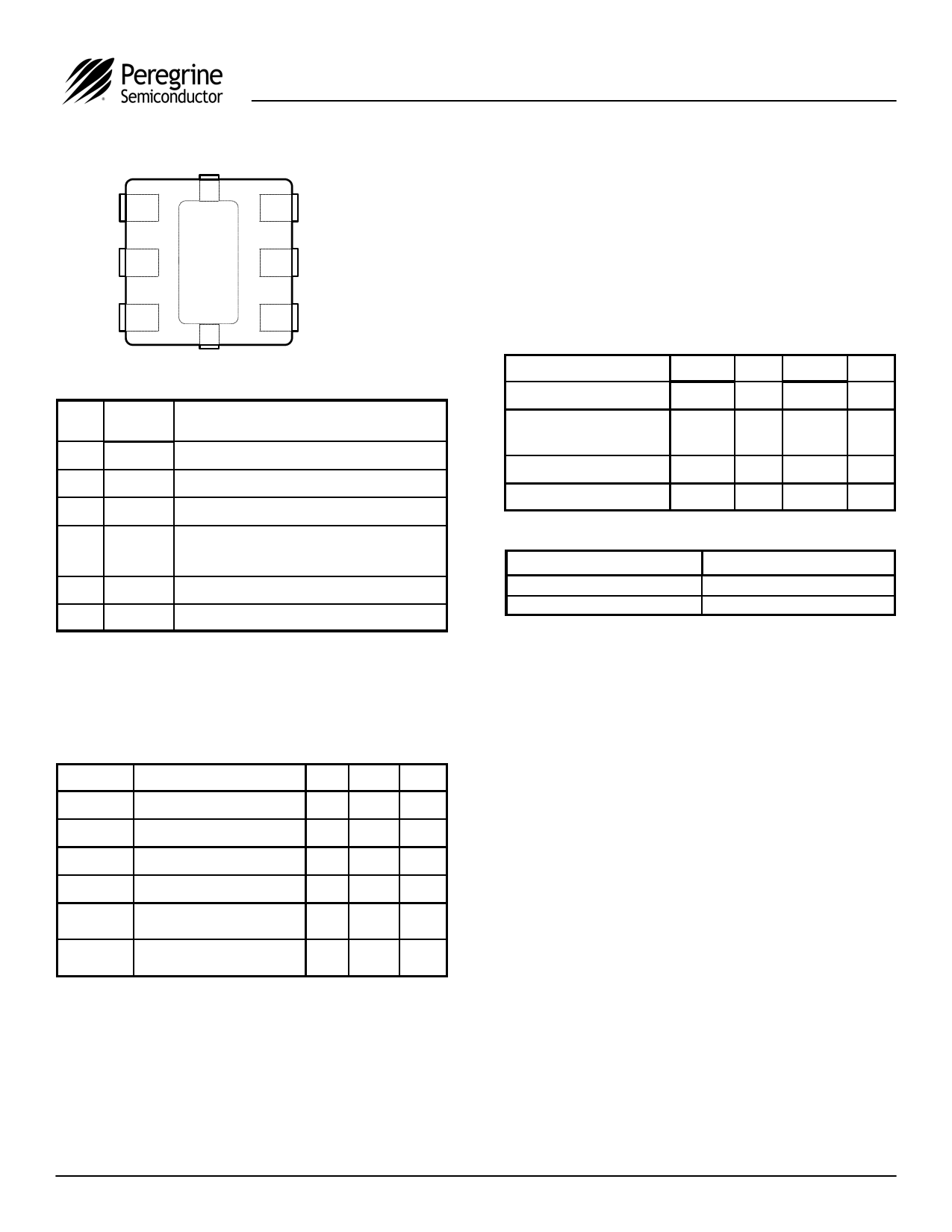

Figure 3. Pin Configuration

VDD 1

GND 2

RF1 3

Exposed

Solder Pad

(bottom side)

6 RF2

5 GND

4 CTRL

Table 2. Pin Descriptions

Pin

Pin

No. Name

Description

1

VDD

Nominal 3 V supply connection.1

2

GND Ground connection. 3

3

RF1

RF port. 2

CMOS or TTL logic level:

4

CTRL

High = RF1 to RF2 signal path

Low = RF1 isolated from RF2

5

GND Ground connection. 3

6

RF2

RF port. 2

Notes: 1. A bypass capacitor should be placed as close as possible

to the pin.

2. Both RF pins must be DC blocked by an external capacitor

or held at 0 VDC.

3. The exposed pad must be soldered to the ground plane for

proper switch performance.

Table 3. Absolute Maximum Ratings

Symbol Parameter/Condition Min Max Unit

VDD

VI

TST

TOP

PIN

VESD

Power supply voltage

Voltage on CTRL input

Storage temperature

Operating temperature

Input power (50 Ω),

CTRL=1/CTRL=0

ESD voltage

(Human Body Model)

-0.3 4.0

V

-0.3 5.5

V

-65 150 °C

-40 85

°C

33/24 dBm

200

V

Absolute Maximum Ratings are those values

listed in the above table. Exceeding these values

may cause permanent device damage.

Functional operation should be restricted to the

limits in the DC Electrical Specifications table.

Exposure to absolute maximum ratings for

extended periods may affect device reliability.

©2005 Peregrine Semiconductor Corp. All rights reserved.

Page 2 of 8

PE4246

Product Specification

Device Description

The PE4246 high-isolation SPST RF Switch is

designed to support a variety of applications

where high isolation performance is demanded

and a non-reflective input and output is desired.

This switch is able to replace multiple lesser

performing switches in a very small 3x3 mm DFN

footprint.

Table 4. DC Electrical Specifications

Parameter

Min Typ Max

VDD Power Supply

2.7

3.0

3.3

IDD Power Supply Current

(VDD = 3 V, VCNTL = 3 V)

33

40

Control Voltage High

0.7xVDD

5

Control Voltage Low

0

0.3xVDD

Unit

V

µA

V

V

Table 5. Control Logic Truth Table

Control Voltage

CTRL = CMOS or TTL High

CTRL = CMOS or TTL Low

Signal Path

RF1 to RF2

RF1 isolated from RF2

Control Logic

The control logic input pin (CTRL) is typically

driven by a 3-volt CMOS logic level signal, and

has a threshold of 50% of VDD. For flexibility to

support systems that have 5-volt control logic

drivers, the control logic input has been designed

to handle a 5-volt logic HIGH signal. (A minimal

current will be sourced out of the VDD pin when the

control logic input voltage level exceeds VDD.)

Electrostatic Discharge (ESD) Precautions

When handling this UltraCMOS™ device, observe

the same precautions that you would use with

other ESD-sensitive devices. Although this device

contains circuitry to protect it from damage due to

ESD, precautions should be taken to avoid

exceeding the rating specified in Table 3.

Latch-Up Avoidance

Unlike conventional CMOS devices, UltraCMOS™

devices are immune to latch-up.

Document No. 70-0090-05 │ UltraCMOS™ RFIC Solutions