RT9266PE Ver la hoja de datos (PDF) - Richtek Technology

Número de pieza

componentes Descripción

Lista de partido

RT9266PE Datasheet PDF : 14 Pages

| |||

RT9266

Application Information

Output Voltage Setting

Referring to Typical Application Circuits, the output voltage

of the switching regulator (VOUT) can be set with Equation

(1).

R1

VOUT = ( 1+ ) × 1.25V

(1)

R2

Feedback Loop Design

Referring to Typical Application Circuits. The selection of

R1 and R2 based on the trade-off between quiescent

current consumption and interference immunity is stated

below:

l Follow Equation (1)

l Higher R reduces the quiescent current (Path current

= 1.25V/R2), however resistors beyond 5MΩ are not

recommended.

l Lower R gives better noise immunity, and is less

sensitive to interference, layout parasitics, FB node

leakage, and improper probing to FB pins.

VOUT

Prober Parasitics

_

Q

+

R1

FB Pin

R2

l A proper value of feed forward capacitor parallel with

R1 can improve the noise immunity of the feedback

loops, especially in an improper layout. An empirical

suggestion is around 0~33pF for feedback resistors of

MΩ, and 10nF~0.1µF for feedback resistors of tens to

hundreds kΩ.

For applications without standby or suspend modes,

lower values of R1 and R2 are preferred. For applications

concerning the current consumption in standby or

suspend modes, the higher values of R1 and R2 are

needed. Such “high impedance feedback loops” are

sensitive to any interference, which require careful layout

and avoid any interference, e.g. probing to FB pin.

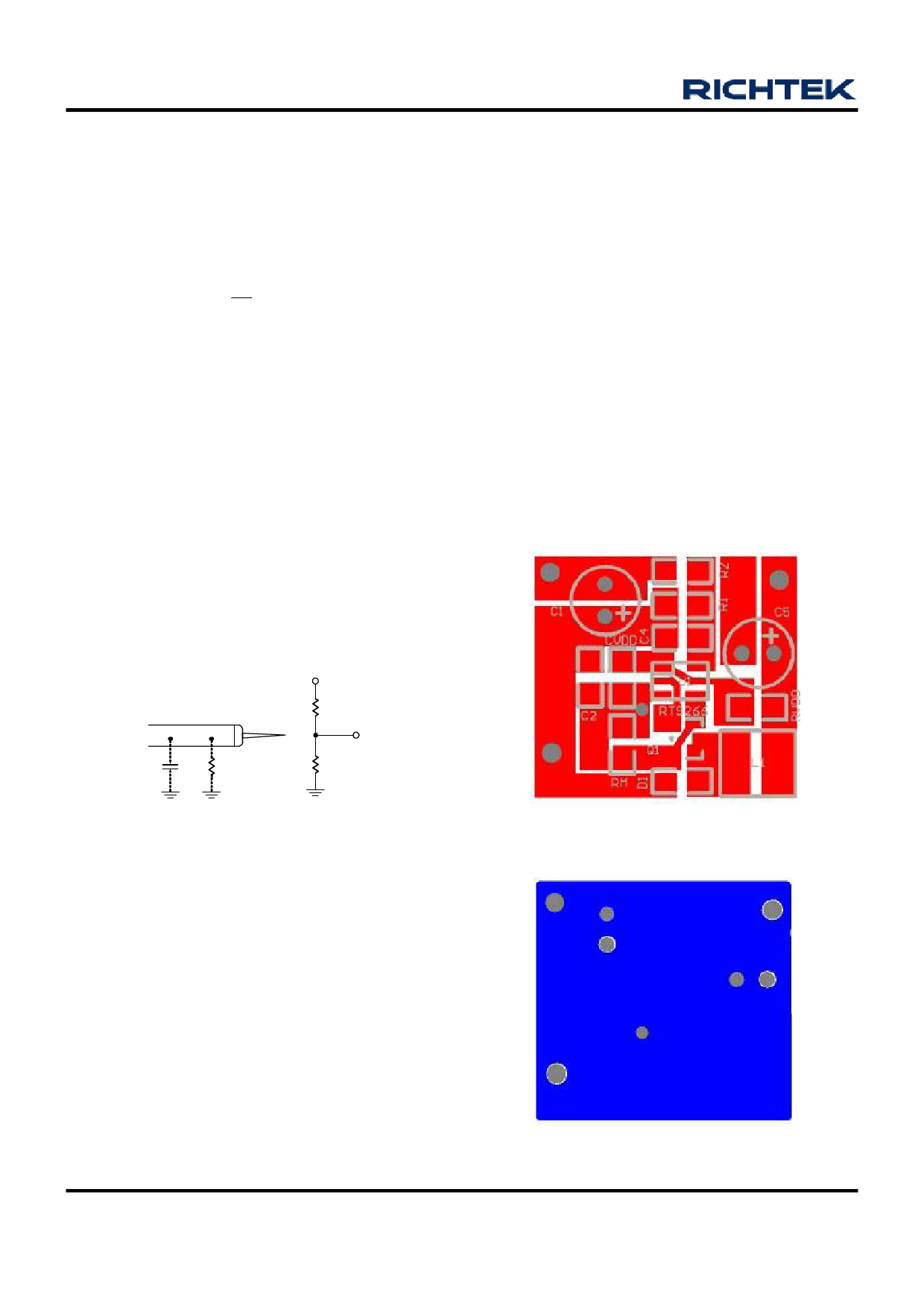

Layout Guide

l A full GND plane without gap break.

l VDD to GND noise bypass − Short and wide connection

for the 1µF MLCC capacitor between Pin5 and Pin3.

l VIN to GND noise bypass − Add a capacitor close to L1

inductor, when VIN is not an idea voltage source.

l Minimized FB node copper area and keep far away

from noise sources.

l Minimized parasitic capacitance connecting to LX and

EXT nodes, which may cause additional switching loss.

Board Layout Example (2-Layer Board)

(Refer to Typical Application Circuits Figure 2 for the board)

- Top Layer -

www.richtek.com

12

- Bottom Layer -

DS9266-12 May 2007