SAA4952WP Ver la hoja de datos (PDF) - Philips Electronics

Número de pieza

componentes Descripción

Lista de partido

SAA4952WP Datasheet PDF : 32 Pages

| |||

Philips Semiconductors

Memory controller

Objective specification

SAA4952WP

FEATURES

• Support for acquisition, display and deflection PLL

• 50/100 Hz (or 60/120 Hz) scan conversion

• Progressive scan 50 Hz/1250 lines (60 Hz/1050 lines)

interlaced or 50 Hz/625 lines (60 Hz/525 lines)

non-interlaced in serial memory structure

• 50 Hz/625 lines (60 Hz/525 lines) mode support for a

PALplus system and basic features

• Acquisition frequencies 12, 13.5, 16 and 18 MHz and

display frequencies of 27, 32 and 36 MHz (2fH) in every

combination, horizontal compression (support for 4 : 3

and 14 : 9 display on a 16 : 9 screen) and horizontal

zoom

• Configured as a three clock system with a fixed 27 MHz

deflection clock (deflection controlled by the TDA9151)

• Configured as a two-clock system (deflection controlled

by e.g. TDA9152)

• Single clock for 50 Hz vertical and 15.625 kHz

horizontal frequency

• Support of new IC generations [PAN-IC (SAA4995WP),

VERIC (SAA4997H), MACPACIC (SAA4996H) and

LIMERIC (SAA4945H)]

• Support for two or one field memories

• Still picture

• Support for memory types such as TMS4C2970/71

• Internal simple Multi-PIP (3 × 3) or (4 × 4) conversion

• Multi-PIP support with an external PIP module/full

performance

• Programmable via microcontroller port

• Capability of reading the length of incoming fields via

microcontroller port

• Golden SCART option (clock generation for TDA9151)

• Acquisition is able to operate with external sync and

clock of digital sources (slave mode)

• Generator mode for the display, stable still picture or

OSD in the event of no input source.

GENERAL DESCRIPTION

The memory controller SAA4952WP is the improved

version of the SAA4951WP. The circuit has been designed

for high-end TV sets using 2fH technics. For basic feature

modules a 1fH mode can be activated. In this situation the

controller supplies the system with a line-locked clock.

The new device has been designed to be able to operate

in the hardware environment of the SAA4951WP.

The circuit provides all necessary write, read and clock

pulses to control different field memory concepts.

Furthermore the drive signals for the horizontal and

vertical deflection power stages are also generated.

The device is connected to a microcontroller via an 8-bit

data bus. The microcontroller receives commands via the

I2C-bus. Due to this fact the START and STOP conditions

of the main output control signals are programmable and

the SAA4952WP can be set in different function modes

depending on the TV feature concept that is used.

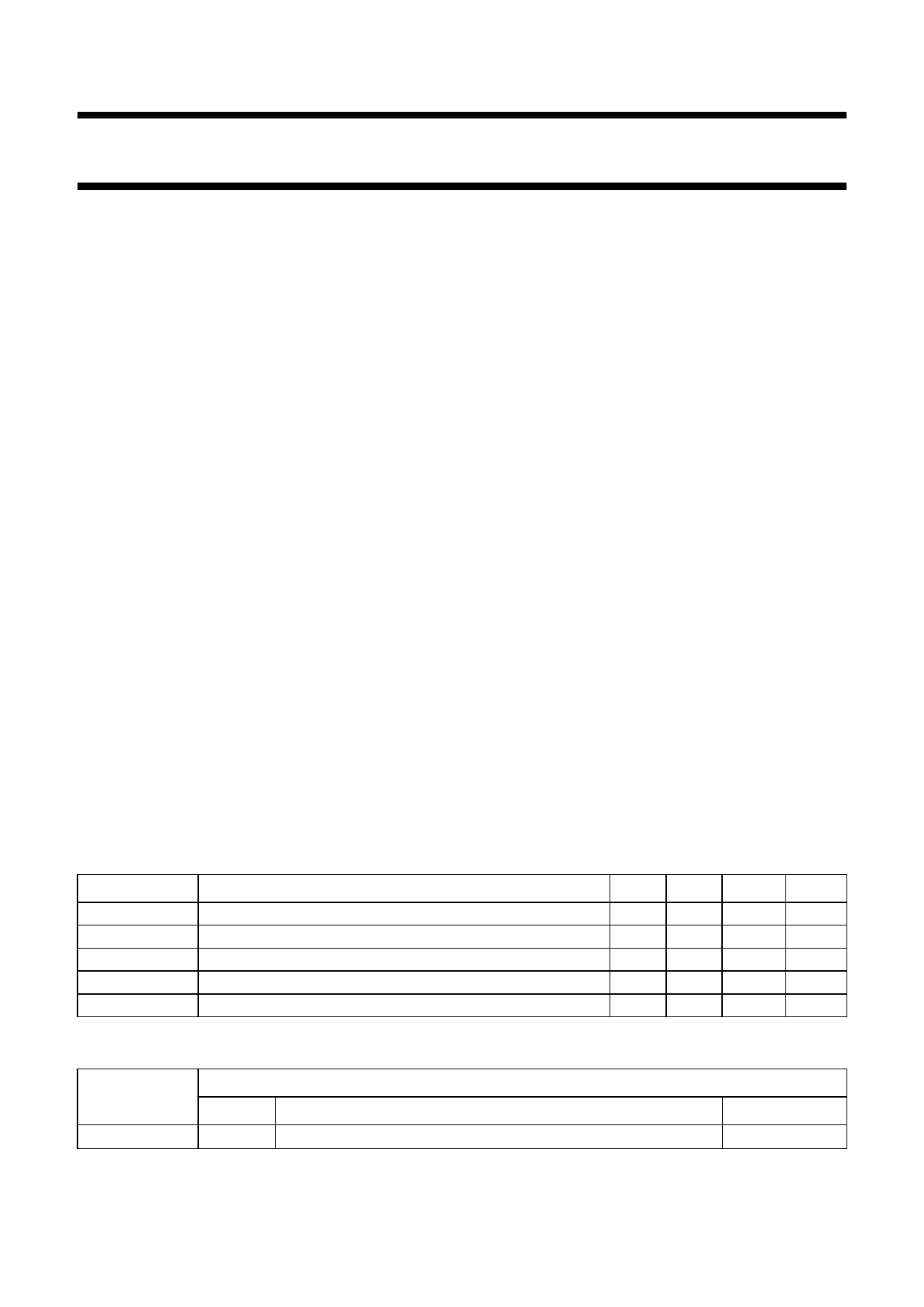

QUICK REFERENCE DATA

SYMBOL

VDD

IDD

fLLDFL,LLD

facq

Tamb

PARAMETER

supply voltage

supply current

operating frequency of display and deflection part

acquisition frequency

operating ambient temperature

MIN.

4.5

−

−

−

0

TYP.

5

35

−

−

−

MAX.

5.5

−

33

37

85

UNIT

V

mA

MHz

MHz

°C

ORDERING INFORMATION

TYPE NUMBER

SAA4952WP

NAME

PLCC44

PACKAGE

DESCRIPTION

plastic leaded chip carrier; 44 leads

VERSION

SOT187-2

1997 Jun 10

2