RF2607 Ver la hoja de datos (PDF) - RF Micro Devices

Número de pieza

componentes Descripción

Lista de partido

RF2607 Datasheet PDF : 8 Pages

| |||

RF2607

Pin

1

2

3

4

Function

CDMA+

Description

CDMA balanced input pin. This pin is internally DC-biased and should

be DC blocked if connected to a device with a DC level other than VCC

present. A DC to connection to VCC is acceptable. For single-ended

input operation, one pin is used as an input and the other CDMA input

is AC-coupled to ground. The balanced input impedance is 1kΩ, while

the single-ended input impedance is 500Ω.

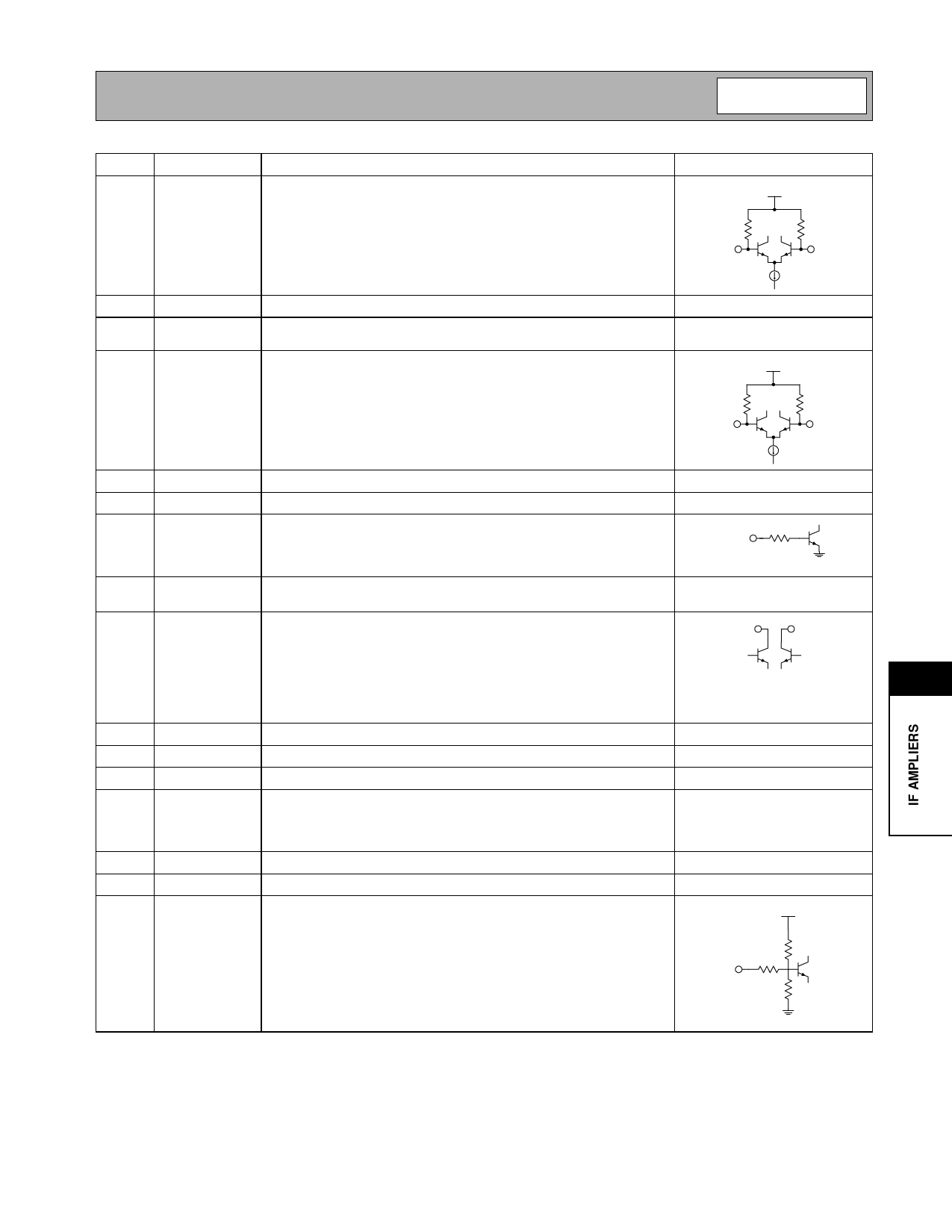

Interface Schematic

BIAS

CDMA+

700 Ω

700 Ω

CDMA-

CDMA-

GND

FM+

Same as pin 2, except complementary input.

See pin 1.

Ground connection. For best performance, keep traces physically short

and connect immediately to ground plane.

FM balanced input pin. This pin is internally DC-biased and should be

DC blocked if connected to a device with DC present. For single-ended

input operation, one pin is used as an input and the other FM input is

AC-coupled to ground. The balanced input impedance is 1.7kΩ, while

the single-ended input impedance is 850Ω.

BIAS

FM+

650 Ω

650 Ω

FM-

5

FM-

Same as pin 4, except complementary input.

See pin 4.

6

GND

Same as pin 3.

7

IN SELECT Selects which IF input (CDMA or FM) is used. This is a digitally con-

trolled input. A logic "high" selects the CDMA input amplifier. A logic

"low" selects the FM input amplifier. The threshold voltage is approxi-

mately 1.3V.

IN SELECT

20 kΩ

8

NC

No Connection pin. This pin is internally biased and should not be con-

nected to any external circuitry, including ground or VCC.

9

OUT-

Balanced output pin. This is an open-collector output, designed to

operate into a 250Ω balanced load. The load sets the operating imped-

OUT+

OUT-

ance, but an external choke or matching inductor to VCC must also be

supplied in order to correctly bias this output. This bias inductor is typi-

cally incorporated in the matching network between the output and next

stage. Because this pin is biased to VCC, a DC-blocking capacitor must

be used if the next stage’s input has a DC path to ground.

10

OUT+

Same as pin 9, except complementary output.

See pin 9.

11

GND

Same as pin 3.

12

GND

Same as pin 3.

13

VCC

Supply voltage pin. External bypassing is required. The trace length

between the pin and the bypass capacitors should be minimized. The

ground side of the bypass capacitors should connect immediately to

ground plane.

14

VCC

Same as pin 13.

15

VCC

Same as pin 13.

16

GC

Analog gain adjustment for all amplifiers. Valid control ranges are from

0V to 3.0V. Maximum gain is selected with 3.0V. Minimum gain is

selected with 0V. These voltages are only valid for a 4.7kΩ DC source

impedance.

VCC

12.7 kΩ

23.5 kΩ

15 kΩ

10

Rev B2 010720

10-3