IMIZ9972 Ver la hoja de datos (PDF) - Cypress Semiconductor

Número de pieza

componentes Descripción

Lista de partido

IMIZ9972 Datasheet PDF : 9 Pages

| |||

Z9972

Power Management

The individual output enable/freeze control of the Z9972

allows the user to implement unique power management

schemes into the design. The outputs are stopped in the logic

“0” state when the freeze control bits are activated. The serial

input register contains one programmable freeze enable bit for

12 of the 14 output clocks. The QC0 and FB_OUT outputs can

not be frozen with the serial port, this avoids any potential lock

up situation should an error occur in the loading of the serial

data. An output is frozen when a logic “0” is programmed and

enabled when a logic “1” is written. The enabling and freezing

of individual outputs is done in such a manner as to eliminate

the possibility of partial “runt” clocks.

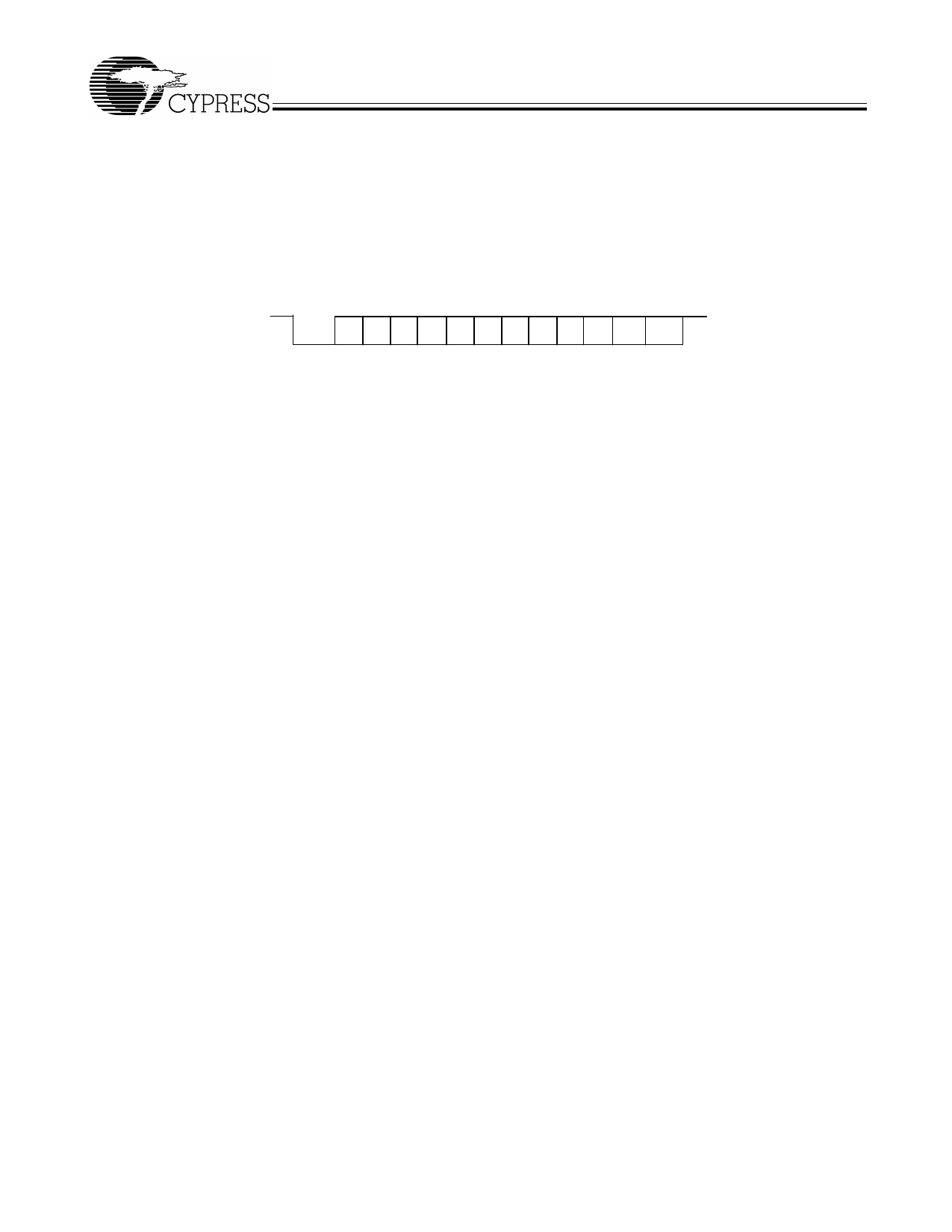

The serial input register is programmed through the SDATA

input by writing a logic “0” start bit followed by 12 NRZ freeze

enable bits. The period of each SDATA bit equals the period of

the free running SCLK signal. The SDATA is sampled on the

rising edge of SCLK.

Start

Bit

D0 D1 D2 D3 D4 D5 D6 D7 D8 D9 D10 D11

D0-D3 are the control bits for QA0-QA3, respectively

D4-D7 are the control bits for QB0-QB3, respectively

D8-D10 are the control bits for QC1-QC3, respectively

D11 is the control bit for SYNC

Figure 2. SDATA Input Register

Document #: 38-07088 Rev. *D

Page 5 of 9