IMIZ9974 Ver la hoja de datos (PDF) - Cypress Semiconductor

Número de pieza

componentes Descripción

Lista de partido

IMIZ9974 Datasheet PDF : 7 Pages

| |||

Z9974

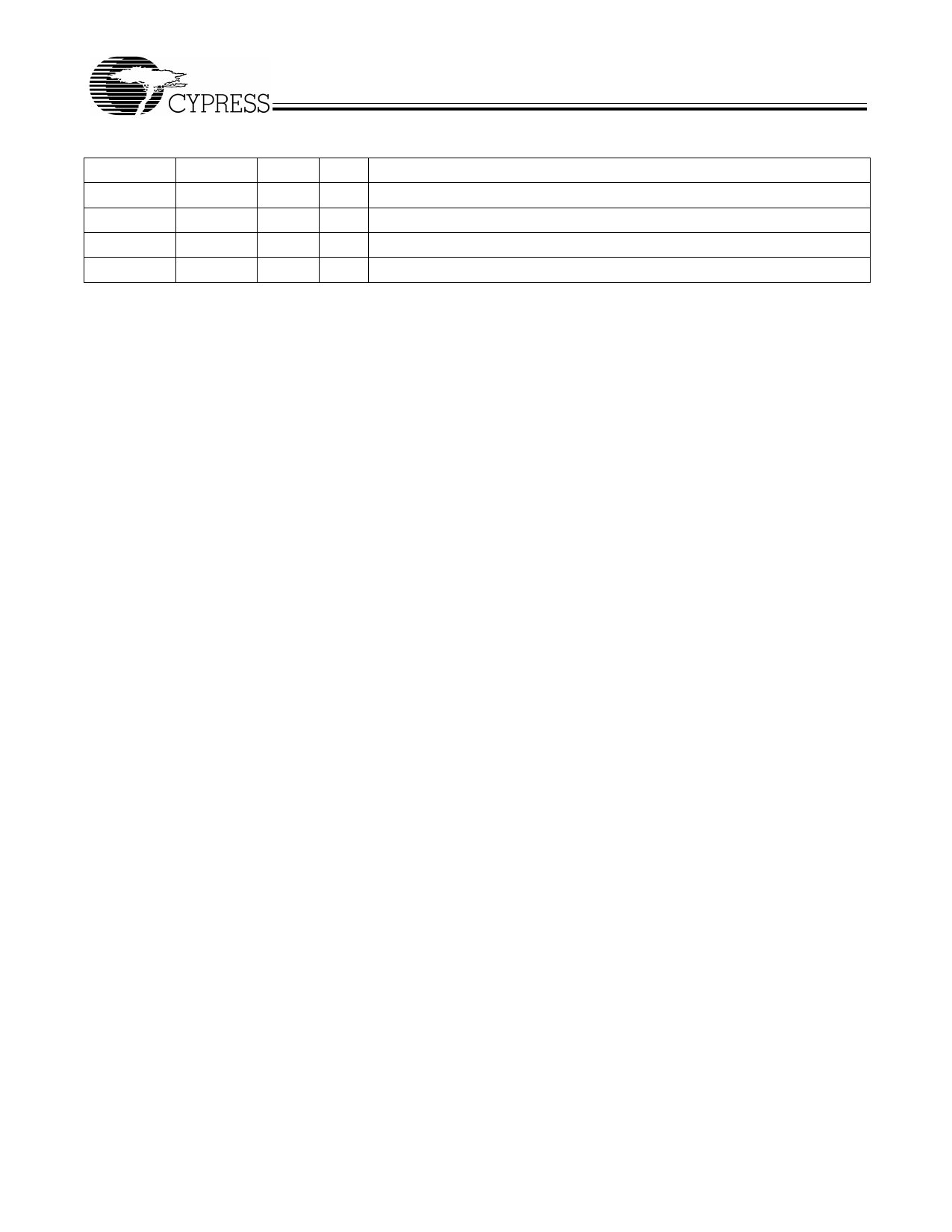

Pin Description[1] (continued)

Pin

Name

PWR

35,39

VSSb

45,49

VDDc

43,47,51

VSSc

1

VSSA

I/O

P

P

P

P

Description

Common ground for Qb(0:4) output bank.

3.3V supply for Qc(0:3) output bank and VCO_sel pin.

Common ground for Qc(0:3) output bank and VCO_sel pin.

Analog Ground

Glitch-Free Output Frequency Transitions

Customarily when zero delay buffers have their internal

counters change “on the fly” their output clock periods will:

1. Contain short or “runt” clock periods. These are clock cycles

in which the cycle(s) are shorter in period than either the

old or new frequency that is being transitioned to.

2. Contain stretched clock periods. These are clock cycles in

which the cycle(s) are longer in period than either the old

or new frequency that is being transitioned to.

This device specifically includes logic to guarantee that runt

and stretched clock pulses do not occur if the device logic

levels of any or all of the following pins changed “on the fly”

while it is operating: Fsela, Fselb, Fselc, and VCO_Sel

Document #: 38-07090 Rev. *C

Page 4 of 7