ST16C552 Ver la hoja de datos (PDF) - Exar Corporation

Número de pieza

componentes Descripción

Lista de partido

ST16C552 Datasheet PDF : 39 Pages

| |||

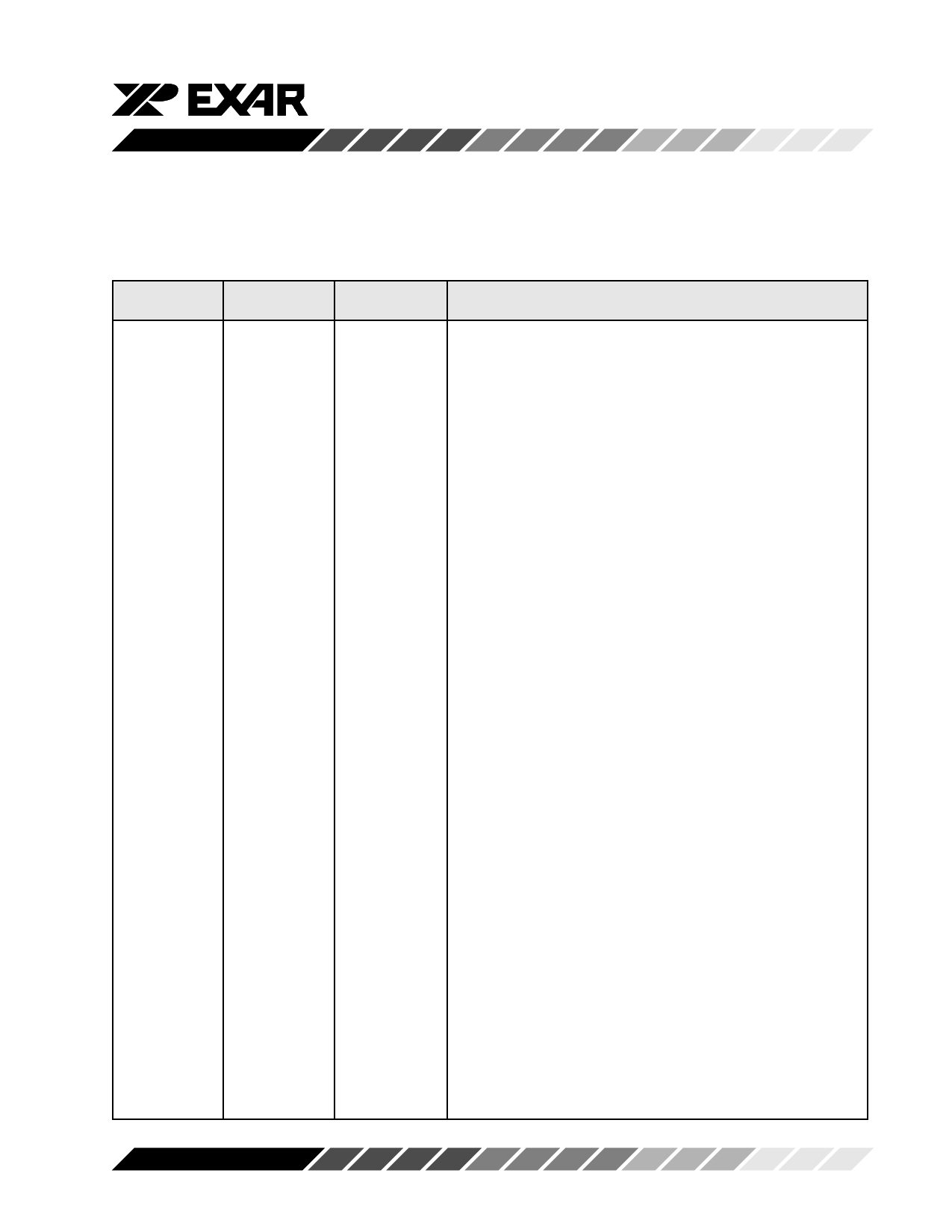

ST16C552/552A

SYMBOL DESCRIPTION

Symbol

-IOR

-IOW

PD7-PD0

PE

RDOUT

-RESET

-RXRDY A/B

Rev. 3.40

Pin

37

36

46-53

67

44

39

9,61

Signal Type

Pin Description

trailing edge of -IOR (end of the external CPU read cycle).

I

Read strobe.- A logic 0 transition on this pin will place the

contents of an Internal register defined by address bits A0-

A2 for either UART channels A/B or A0-A1 for the printer

port, onto D0-D7 data bus for a read cycle by an external

CPU.

I

Write strobe.- A logic 0 transition on this pin will transfer the

data on the internal data bus (D0-D7), as defined by either

address bits A0-A2 for UART channels A/B or A0-A1 for the

printer port, into an internal register during a write cycle from

an external CPU.

I/O

Printer Data port (Bi-directional three state) - These pins are

the eight bit, three state data bus for transferring information

to or from an external device (usually a printer). D0 is the

least significant bit. PD7-PD0 are latched during a write

cycle (output mode).

I

Paper Empty - General purpose input or line printer paper

empty (Internal pull-up). This pin can be connected to

provide a printer out of paper indication.

O

Read Out (active high) - This pin goes to a logic 1 when the

external CPU is reading data from the 552/552A. This signal

can be used to enable/disable external transceivers or other

logic functions.

I

Master Reset (active low) - a logic 0 on this pin will reset the

internal registers and all the outputs. The UART transmitter

output and the receiver input will be disabled during reset

time. (See ST16C552/552A External Reset Conditions for

initialization details.)

O

Receive Ready A/B (active low). This function is associated

with the dual channel UARTs and provide the RX FIFO/

RHR status for individual receive channels (A-B). A logic 0

indicates there is receive data to read/unload, i.e., receive

ready status with one or more RX characters available in the

FIFO/RHR. This pin is a logic 1 when the FIFO/RHR is

empty or when the programmed trigger level has not been

5