ICS9248G-162-T Ver la hoja de datos (PDF) - Integrated Circuit Systems

Número de pieza

componentes Descripción

Lista de partido

ICS9248G-162-T

ICS9248G-162-T Datasheet PDF : 16 Pages

| |||

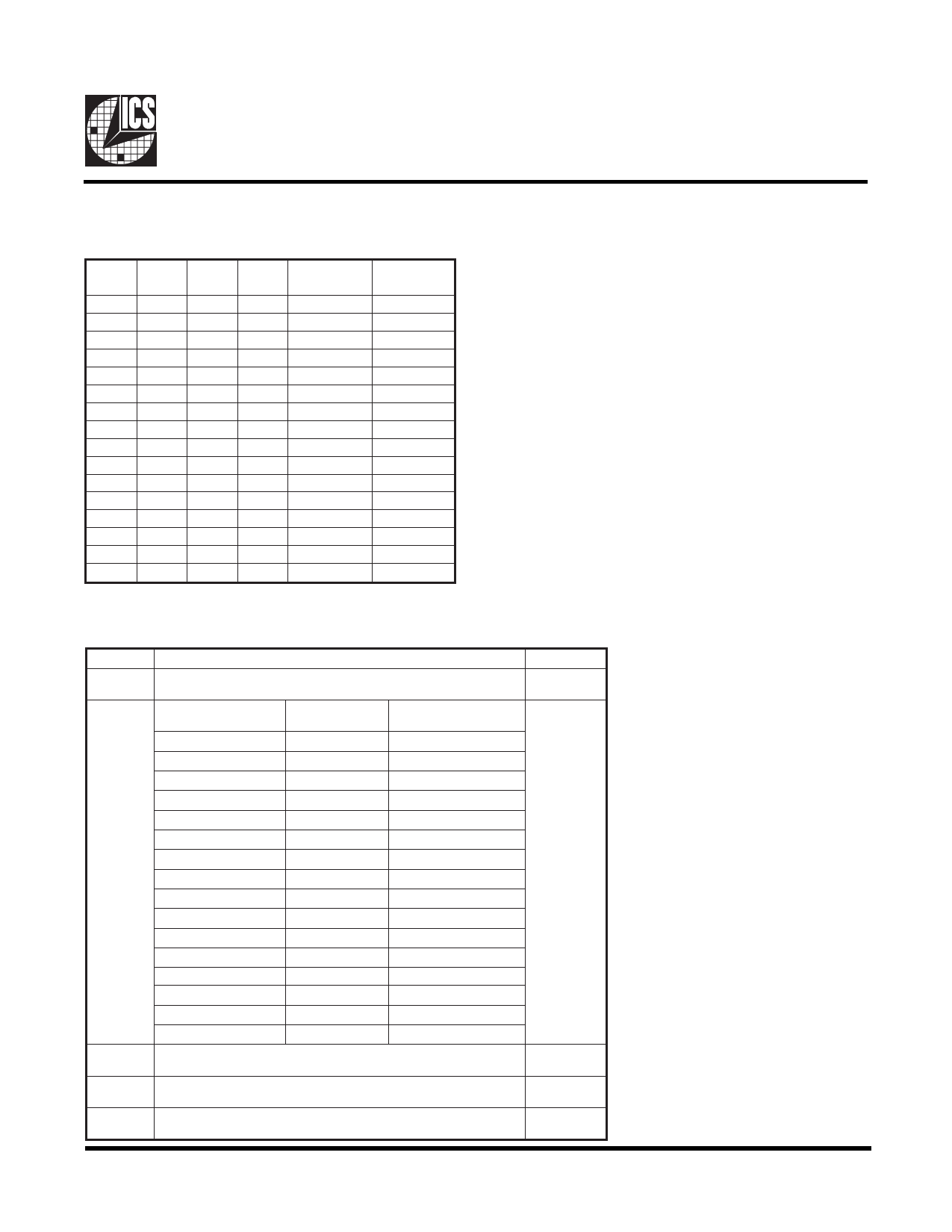

ICS9248 - 162

Functionality

VDD = 3.3V±5%, VDDL= 2.5V±5% or 3.3±5%, TA=0 to 70°C

Crystal (X1, X2) = 14.31818MHz

FS3 FS2 FS1 FS0

0

0

0

0

0

0

0

1

0

0

1

0

0

0

1

1

0

1

0

0

0

1

0

1

0

1

1

0

0

1

1

1

1

0

0

0

1

0

0

1

1

0

1

0

1

0

1

1

1

1

0

0

1

1

0

1

1

1

1

0

1

1

1

1

CPU

(MHz)

124.00

120.00

114.99

109.99

105.00

83.31

137.00

75.00

100.00

95.00

97.00

133.33

90.00

96.22

66.82

91.5

PCI

(MHz)

41.33

40.00

38.33

36.66

35.00

41.65

34.25

37.50

33.33

31.67

32.33

33.33

30.00

32.07

33.41

30.5

Serial Configuration Command Bitmap

Byte0: Functionality and Frequency Select Register (default = 0)

Bit

Bit 7

Bit

[2, 6:4]

Bit 3

Bit 1

Bit 0

Description

0 - ±0.25% Spread Spectrum Modulation, Center Spread

1 - 0 to -0.5% Down Spread

Bit [2, 6:4]

CPUCLK

(MHz)

PCICLK

(MHz)

0000

124.00

41.33

0001

120.00

40.00

0010

114.99

38.33

0011

109.99

36.66

0100

105.00

35.00

0101

83.31

41.65

0110

137.00

34.25

0111

75.00

37.50

1000

100.00

33.33

1001

95.00

31.67

1010

97.00

32.33

1011

133.33

33.33

1100

90.00

30.00

1101

96.22

32.07

1110

66.82

33.41

1111

91.5

30.5

0 - Frequency is selected by hardware select, latched inputs

1 - Frequency is selected by Bit (2, 6:4)

0 - Normal

1 - Spread Spectrum Enabled

0 - Running

1- Tristate all outputs

PWD

1

Note1

0

1

0

Notes:

1, Default at Power-up will be for latched

logic inputs to define frequency.

Bit (2, 6:4) are default to 0010.

2, PWD = Power-Up Default

3, When disabling spread spectrum bit7

needs to be set to 0 to maintain nominal

frequency.

3