IDT7024S15PF Ver la hoja de datos (PDF) - Integrated Device Technology

Número de pieza

componentes Descripción

Lista de partido

IDT7024S15PF Datasheet PDF : 20 Pages

| |||

IDT7024S/L

HIGH-SPEED 4K x 16 DUAL-PORT STATIC RAM

MILITARY AND COMMERCIAL TEMPERATURE RANGES

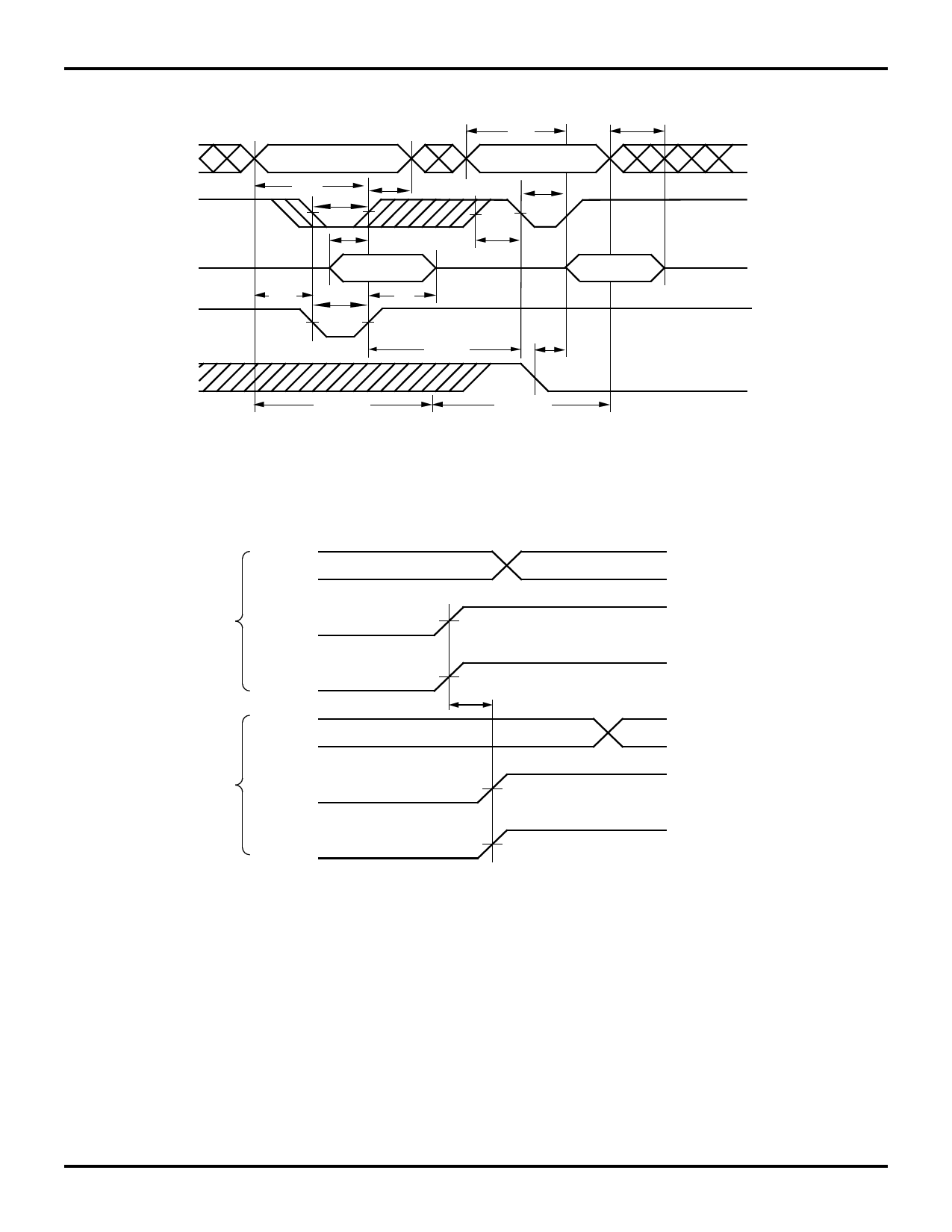

TIMING WAVEFORM OF SEMAPHORE READ AFTER WRITE TIMING, EITHER SIDE(1)

A0-A2

SEM

I/O0

R/W

VALID ADDRESS

tAW

tWR

tEW

tDW

DATAIN

VALID

tAS

tWP

tDH

tSAA

tOH

VALID ADDRESS

tACE

tSOP

DATAOUT

VALID(2)

tSWRD

tAOE

OE

Write Cycle

Read Cycle

NOTES:

1. CE = VIH or UB & LB = VIH for the duration of the above timing (both write and read cycle).

2. "DATAOUT VALID" represents all I/O's (I/O0-I/O15) equal to the semaphore value.

2740 drw 11

TIMING WAVEFORM OF SEMAPHORE WRITE CONTENTION(1,3,4)

A0"A"-A2"A"

MATCH

SIDE(2) “A”

W R/ "A"

SEM"A"

A0"B"-A2"B"

SIDE(2) “B”

W R/ "B"

tSPS

MATCH

SEM"B"

2740 drw 12

NOTES:

1. D0R = D0L = VIL, CER = CEL = VIH, or both UB & LB = VIH, Semaphore Flag is released from both sides (reads as ones from both sides) at cycle start.

2. All timing is the same for left and right ports. Port “A” may be either left or right port. Port “B” is the opposite from port “A”.

3. This parameter is measured from R/WA or SEMA going High to R/WB or SEMB going High.

4. If tSPS is not satisfied, there is no guarantee which side will be granted the Semaphore flag.

6.15

11