MB86615 Ver la hoja de datos (PDF) - Fujitsu

Número de pieza

componentes Descripción

Lista de partido

MB86615 Datasheet PDF : 48 Pages

| |||

MB86615

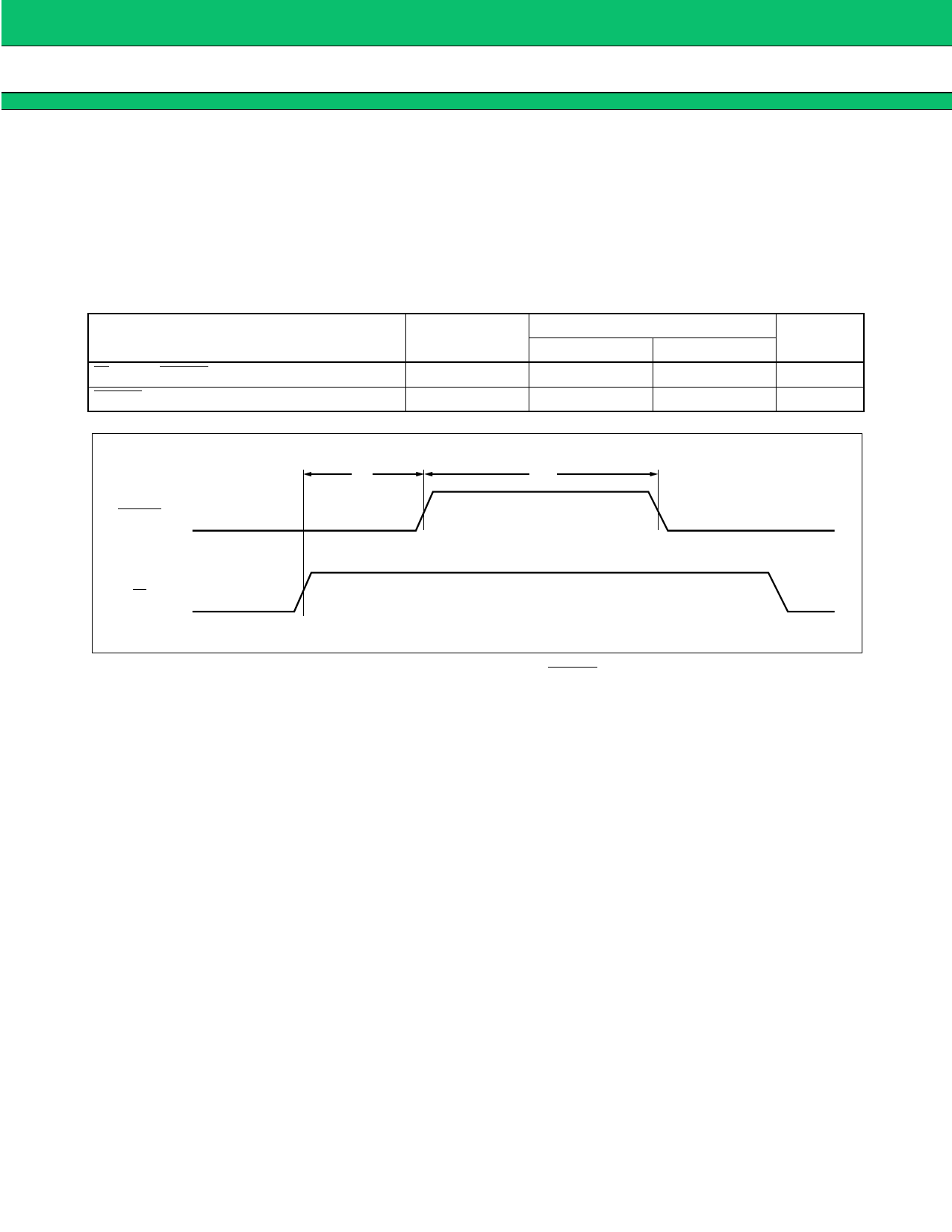

2.6.4 Clearing the ISO Transmission/Reception FIFO Buffer Using the fifo-clr Bit

The ISO transmission/reception FIFO buffer is cleared by setting the fifo-clr bit (bit 4) in the ISO-FIFO control

register (address 0Eh) to “1.” Given below is a timing chart for the isochronous interface when the FIFO buffer

is cleared.

Note that this FIFO buffer clear function is available only when the point-rec bit (bit 7) or length-chk bit (bit 6)

in the ISO-FIFO control register has been set to “1.”

Parameter

IV rise to ILWRE rise

ILWRE negate time

Symbol

tCLR

tWREH

Min.

—

—

Value

Max.

4 tICLK

7 tICLK

Unit

ns

ns

ILWRE

tCLR

tWREH

IV

* : The ISO transmission/reception FIFO buffer is cleared while the ILWRE signal is negated.

41