78Q8430 Ver la hoja de datos (PDF) - Maxim Integrated

Número de pieza

componentes Descripción

Lista de partido

78Q8430 Datasheet PDF : 88 Pages

| |||

DS_8430_001

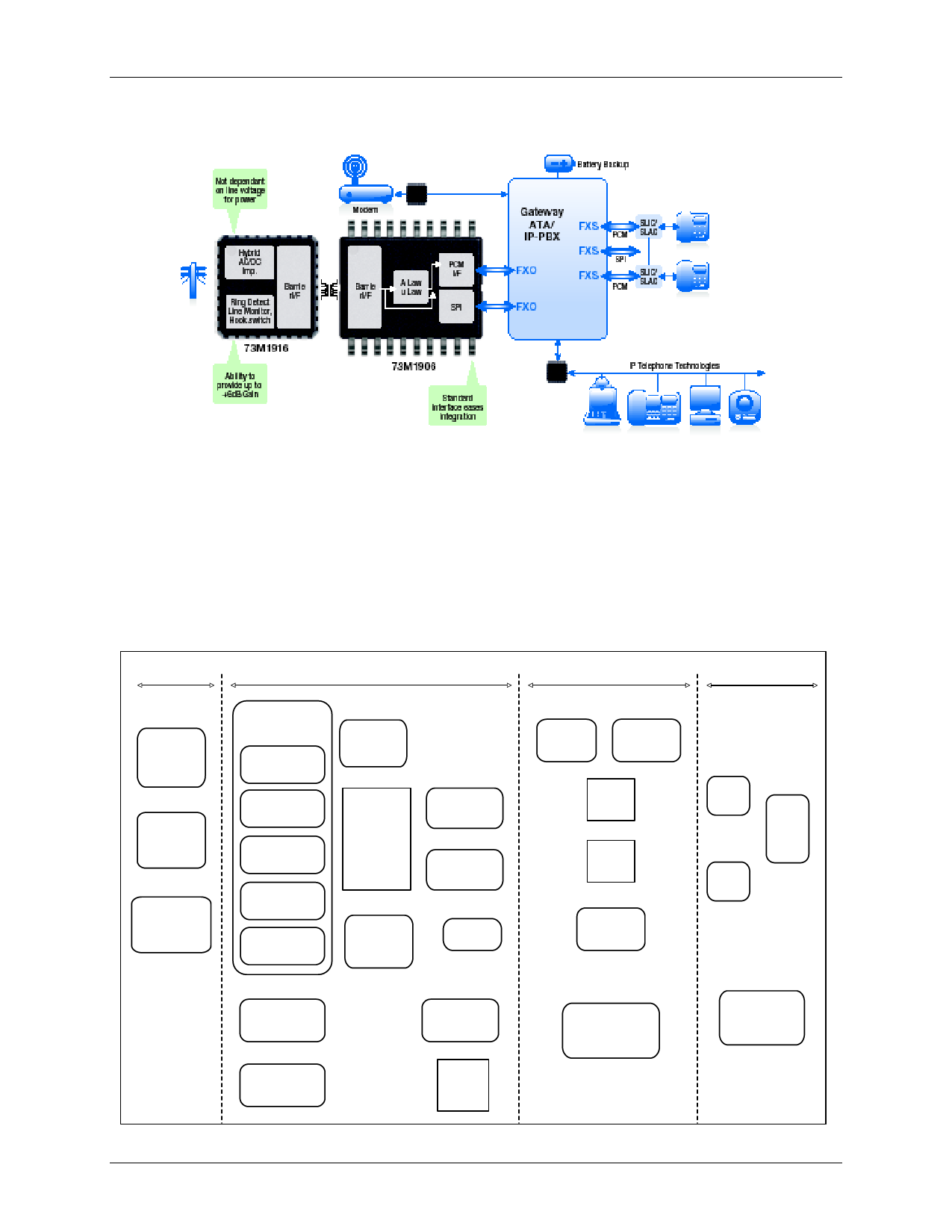

1.2.3 IP PBX Application

Figure 4 shows a typical application diagram for an IP PBX application.

78Q8430

10/100 MAC/PHY

78Q8430 Data Sheet

78Q8430

10/100 MAC/PHY

Figure 4: Typical FXO VoIP Application

1.3 Overview

The 78Q8430 is divided into four sections, as shown in Figure 5.

• Generic Bus Interface (GBI) Control Layer

• Queue Memory Layer

• Ethernet Media Access Control (MAC) Layer

• Ethernet Physical (PHY) Layer

GBI Bus Layer

GBI

Access

Logic

GBI

DMA Slave

Mode Logic

Queue Memory Layer

QUE

Controller

QUE Write

Logic

QUE Write

Logic

QUE Write

Logic

QUE Write

Logic

QUE Read

Logic

Memory

Manager

QUEUE

SRAM

Pause/

HNR

Timers

MAC Write

Logic

MAC Read

Logic

RMON

Snoop

Controller

CTL

Controller

Packet

Classify

CAM

MAC Layer

PHY Layer

Flow

Control

MAC TX

Logic

TX

FIFO

RX

FIFO

MAC RX

Logic

TX

PCS

PMD

RX

PCS

MAC Control

& Status

Registers

SMI Control

& Status

Register

Figure 5: Device Block Diagram

Rev. 1.2

9