CDB4327 Ver la hoja de datos (PDF) - Cirrus Logic

Número de pieza

componentes Descripción

Lista de partido

CDB4327 Datasheet PDF : 36 Pages

| |||

CS4327

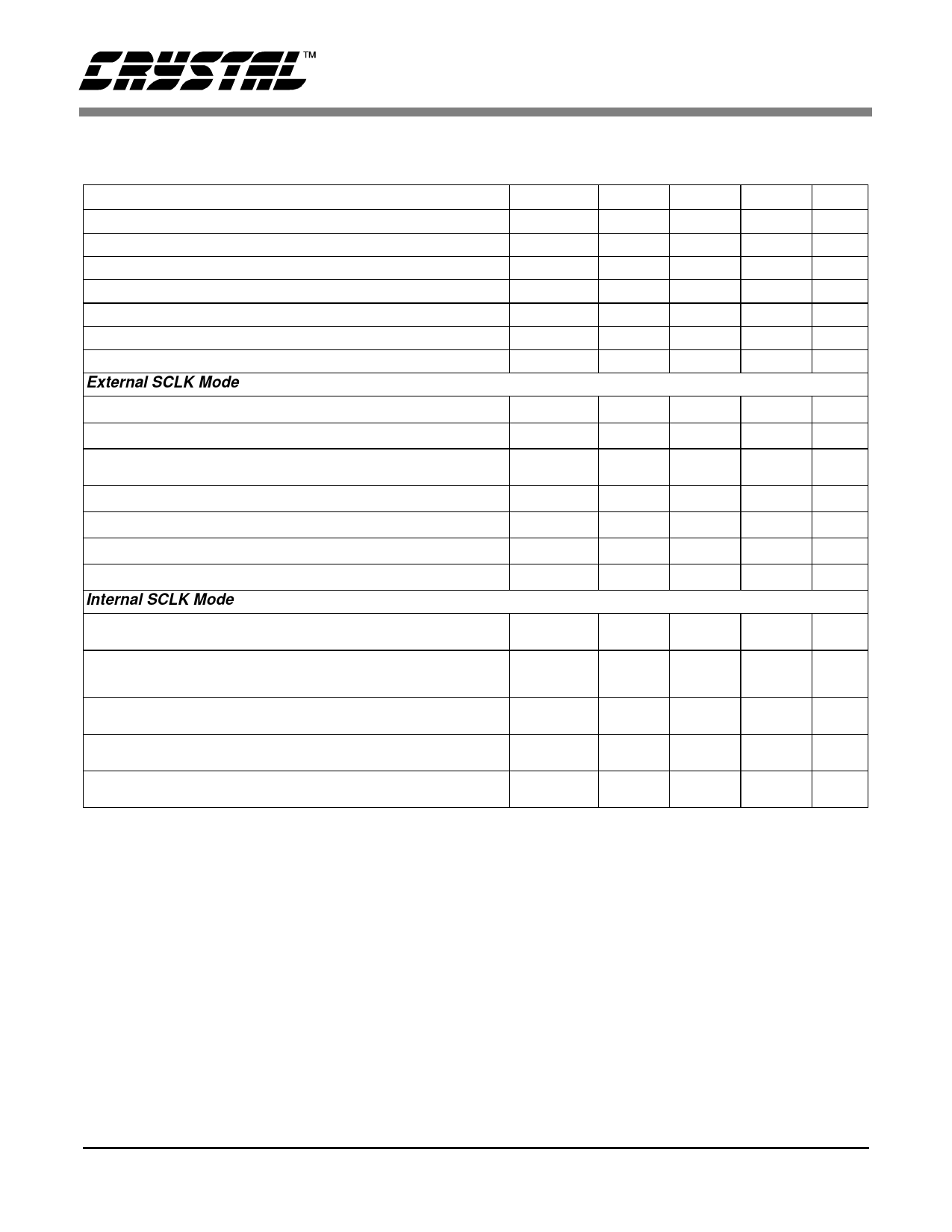

SWITCHING CHARACTERISTICS (TA = 25 °C; VA+ = 5.0 V; Inputs: Logic 0 = 0 V, Logic 1 = VD+,

CL = 20 pF)

Parameter

Input Sample Rate

MCLK Pulse Width High

MCLK Pulse Width Low

MCLK Pulse Width High

MCLK Pulse Width Low

MCLK Pulse Width High

MCLK Pulse Width Low

External SCLK Mode

SCLK Pulse Width Low

SCLK Pulse Width High

SCLK Period

MCLK/LRCK = 512

MCLK/LRCK = 512

MCLK/LRCK = 384

MCLK/LRCK = 384

MCLK/LRCK = 256

MCLK/LRCK = 256

Symbol

Fs

tsclkl

tsclkh

tsclkw

SCLK rising to LRCK edge delay

SCLK rising to LRCK edge setup time

SDATA valid to SCLK rising setup time

SCLK rising to SDATA hold time

Internal SCLK Mode

SCLK Period

tslrd

tslrs

tsdlrs

tsdh

SCLK/LRCK = 64 tsclkw

SCLK rising to LRCK edge

tsclkr

Min

1

10

10

21

21

31

31

20

20

---------1-----------

128(Fs)

20

20

20

20

6----4---(-1-F----s---)

-

Typ

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

t---s---c--2-l--k----w--

Max Unit

50

kHz

-

ns

-

ns

-

ns

-

ns

-

ns

-

ns

-

ns

-

ns

-

ns

-

ns

-

ns

-

ns

-

ns

-

ns

-

ns

SDATA valid to SCLK rising setup time

tsdlrs

5----1---2--1-(--F----s----) + 10

-

SCLK rising to SDATA hold time MCLK/LRCK = 256 or 512

tsdh

5----1---2--1-(--F----s----) + 15

-

SCLK rising to SDATA hold time

MCLK/LRCK = 384 tsdh

3----8---4--1-(--F----s----) + 15

-

-

ns

-

ns

-

ns

4

DS190F1