RTL8029AS Ver la hoja de datos (PDF) - Realtek Semiconductor

Número de pieza

componentes Descripción

Lista de partido

RTL8029AS Datasheet PDF : 41 Pages

| |||

RTL8029AS Preliminary

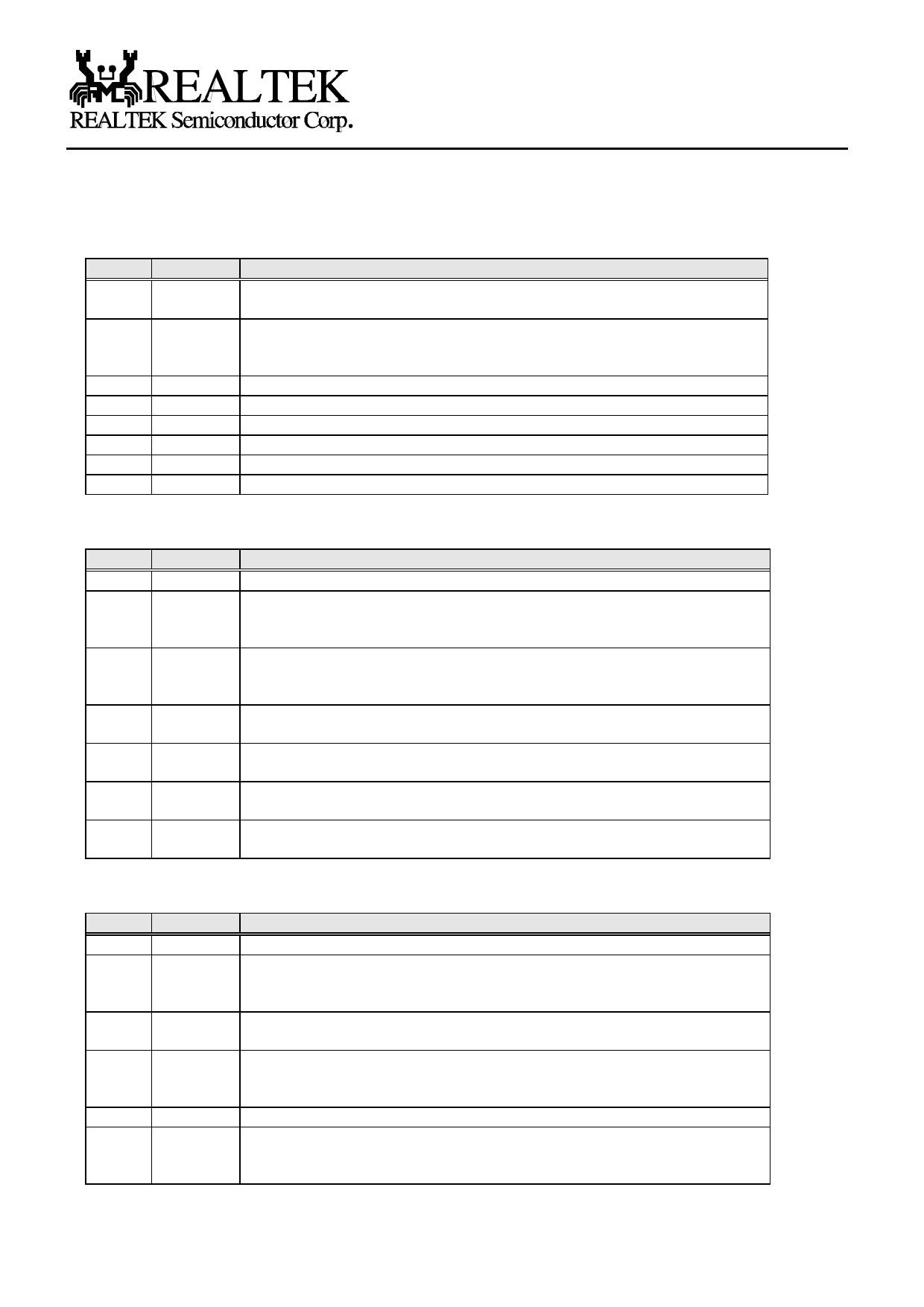

TSR: Transmit Status Register (04H; Type=R in Page0)

This register indicates the status of a packet transmission.

Bit

Symbol

Description

7

OWC Out of Window Collision. It is set when a collision is detected after a slot time

(51.2us). Transmissions are rescheduled as in normal collisions.

6

CDH CD Heartbeat. The NIC watches for a collision signal (i.e., CD Heartbeat signal)

during the first 6.4us of the interframe gap following a transmission. This bit is

set if the transceiver fails to send this signal.

5

-

Always 0.

4

CRS Carrier Sense lost bit is set when the carrier is lost during transmitting a packet.

3

ABT It indicates the NIC aborted the transmission because of excessive collisions.

2

COL It indicates the transmission collided with some other station on the network.

1

-

Always 1.

0

PTX This bit indicates the transmission completes with no errors.

RCR: Receive Configuration Register (0CH; Type=W in Page0, Type=R in Page2)

Bit

Symbol

Description

7, 6

-

Always 1.

5

MON When monitor mode bit is set, received packets are checked for address match,

good CRC and frame alignment but not buffered to memory. Otherwise, packets

will be buffered to memory.

4

PRO If PRO=1, all packets with physical destination address accepted.

If PRO=0, physical destination address must match the node address programmed

in PAR0-5.

3

AM

If AM=1, packets with multicast destination address are accepted.

If AM=0, packets with multicast destination address are rejected.

2

AB

If AB=1, packets with broadcast destination address are accepted.

If AB=0, packets with broadcast destination address are rejected.

1

AR

If AR=1, packets with length fewer than 64 bytes are accepted.

If AR=0, packets with length fewer than 64 bytes are rejected.

0

SEP

If SEP=1, packets with receive errors are accepted.

If SEP=0, packets with receive errors are rejected.

RSR: Receive Status Register (0CH; Type=R in Page0)

Bit

Symbol

Description

7

DFR

Deferring. Set when a carrier or a collision is detected.

6

DIS

Receiver Disabled. When the NIC enters the monitor mode, this bit is set and

receiver is disabled. Reset when receiver is enabled after leaving the monitor

mode.

5

PHY PHY bit is set when the received packet has a multicast or broadcast destination

address. It is reset when the received packet has a physical destination address.

4

MPA Missed Packet bit is set when the incoming packet can not be accepted by NIC

because of a lack of receive buffer or if NIC is in monitor mode. Increment

CNTR2 tally counter.

3

-

Always 0.

2

FAE

Frame Alignment Error bit reflects the incoming packet didn't end on a byte

boundary and CRC did not match at last byte boundary. Increment CNTR0 tally

counter.

LS009.0

15

1997.01.16