RTL8029AS Ver la hoja de datos (PDF) - Realtek Semiconductor

Número de pieza

componentes Descripción

Lista de partido

RTL8029AS Datasheet PDF : 41 Pages

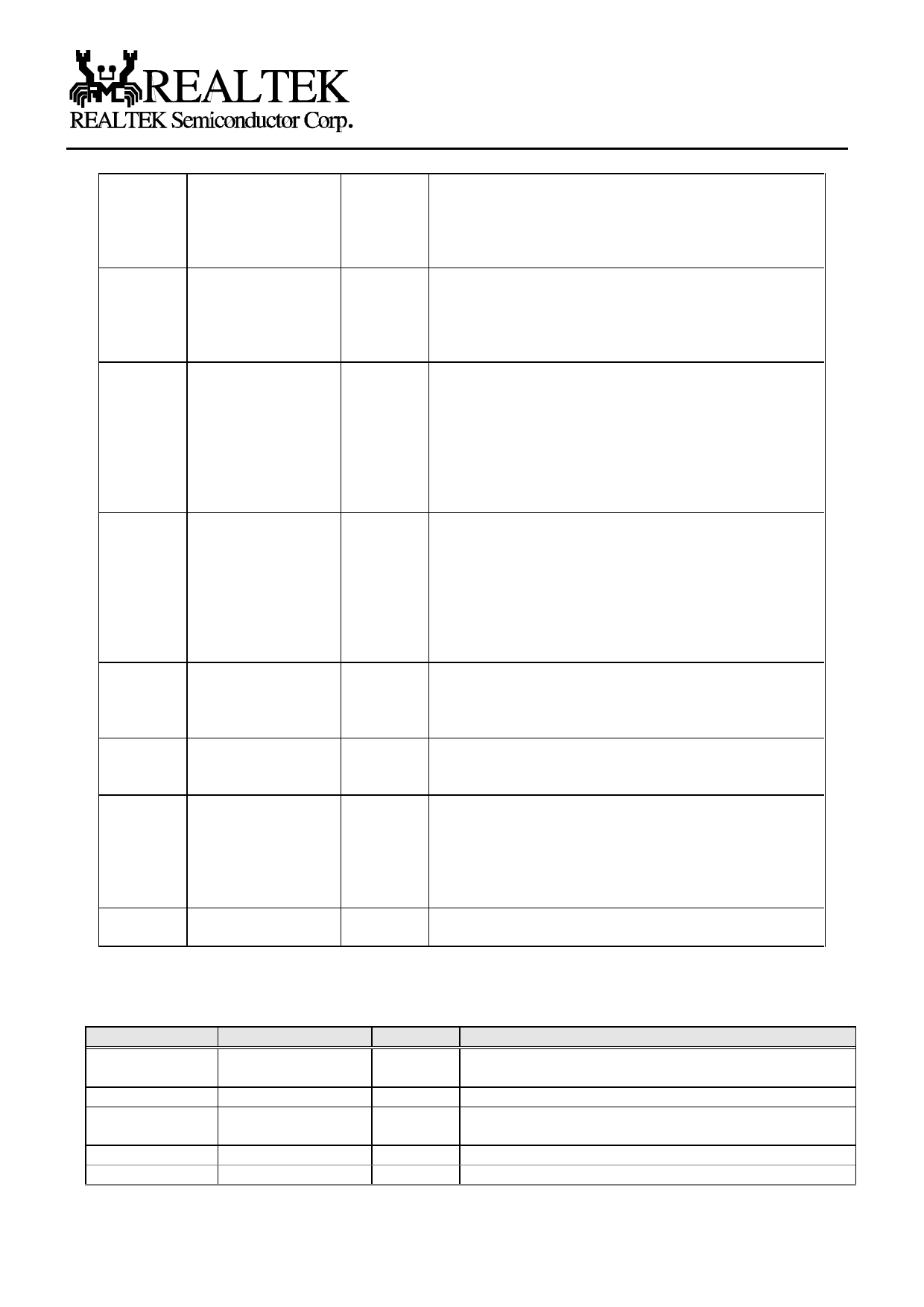

| |||

RTL8029AS Preliminary

18

PAR

T/S

Parity is even parity across AD31-0 and CBE3-0B. PAR is

stable and valid one clock after the address phase. For data

phases PAR is stable and valid one clock after either

IRDYB is asserted on a write transaction or TRDYB is

asserted on a read transaction.

13

FRAMEB

S/T/S Cycle Frame is driven by the current master to indicate the

beginning and duration of an access. FRAMEB is asserted

to indicate a bus transaction is beginning. While FRAMEB

is asserted, data transfers continue. When FRAMEB is

deasserted, the transaction is in the final data phase.

14

IRDYB

S/T/S Initiator Ready indicates the initiating agent's ability to

complete the current data phase of the transaction. IRDYB

is used in conjunction with TRDYB. A data phase is

completed on any clock when both IRDYB and TRDYB are

asserted. During a write, IRDYB indicates that valid data is

present on AD31-0. During a read, it indicates the master is

prepare to accept data. Wait cycles are inserted until both

IRDYB and TRDYB are asserted simultaneously.

15

TRDYB

S/T/S Target Ready indicates the target's agent's ability to

complete the current data phase of the transaction. TRDYB

is used in conjunction with IRDYB. A data phase is

completed on any clock when both TRDYB and IRDYB are

asserted. During a read, TRDYB indicates that valid data is

present on AD31-0. During a write, it indicates the target is

prepare to accept data. Wait cycles are inserted until both

IRDYB and TRDYB are asserted simultaneously.

16

DEVSELB

S/T/S Device Select, when actively driven, indicates the driving

device has decoded its address as the target of the current

access. As an input, DEVSELB indicates whether any

device on the bus has been selected.

2

IDSEL

I

Initialization Device Select is used as a chip select for

RTL8029AS controller during configuration read and write

transaction.

89

RSTB

I

When RSTB is asserted low, the RTL8029AS performs an

internal system hardware reset. RSTB must be held for a

minimum of 120 ns periods. RSTB may be asynchronous to

CLK when asserted or deasserted. It is recommended that

the deassertion be synchronous to guarantee clean and

bounce free edge.

88

INTAB

O/D Interrupt A is an asynchronous attention signal which is

used to request an interrupt.

4.4. Memory Interface Pins (including BROM, EEPROM)

No.

49

50

53

51, 67-54

[57]

Name

BOEB

NC

EECS

MA14-0

[EESK]

Type

O

-

O

O

O

Description

Boot ROM chip select. Active low signal, asserted when

Boot ROM is read.

Unused

9346 chip select. Active high signal, asserted when 9346 is

read/write.

Boot ROM address bus

9346 serial data clock

LS009.0

8

1997.01.16