RTL8201CP-LF Ver la hoja de datos (PDF) - Realtek Semiconductor

Número de pieza

componentes Descripción

Lista de partido

RTL8201CP-LF

RTL8201CP-LF Datasheet PDF : 38 Pages

| |||

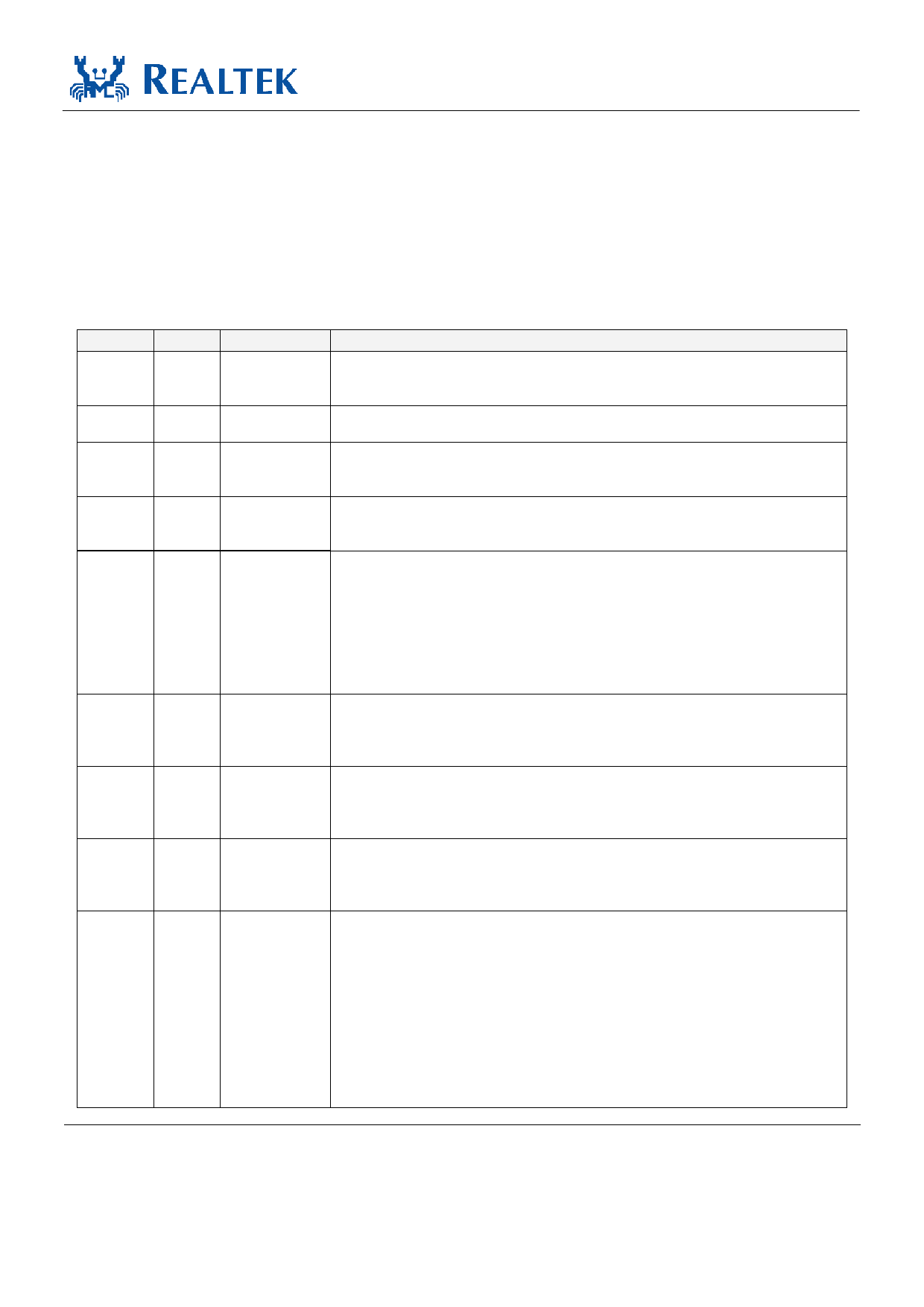

5. Pin Description

LI: Latched Input during Power up or Reset

IO: Bi-directional input and output

RTL8201CP

Datasheet

O: Output

P: Power

I: Input

5.1. MII Interface

Name

TXC

Type

O

TXEN

I

TXD[3:0] I

RXC

O

COL

LI/O

CRS

LI/O

RXDV

O

RXD[3:0] O

RXER/ LI/O

FXEN

Pin No.

7

2

3, 4, 5, 6

16

1

23

22

18, 19, 20, 21

24

Table 1. MII Interface

Description

Transmit Clock.

This pin provides a continuous clock as a timing reference for TXD[3:0] and

TXEN.

Transmit Enable.

The input signal indicates the presence of valid nibble data on TXD[3:0].

Transmit Data.

The MAC will source TXD[0..3] synchronous with TXC when TXEN is

asserted.

Receive Clock.

This pin provides a continuous clock reference for RXDV and RXD[0..3]

signals. RXC is 25MHz in 100Mbps mode and 2.5Mhz in 10Mbps mode.

Collision Detect.

COL is asserted high when a collision is detected on the media.

During power on reset, this pin status is latched to determine at which LED

mode to operate:

0: CP LED mode

1: BL LED mode

An internal weak pull low resistor sets this to the default CP LED mode. It is possible

to use an external 5.1KΩ pull high resistor to enable BL LED mode.

Carrier Sense.

This pin’s signal is asserted high if the media is not in Idle state.

An internal weak pull low resistor sets this to normal operation mode. An external

5.1KΩ pull low resistor could be reserved to ensure operating at normal mode.

Receive Data Valid.

This pin’s signal is asserted high when received data is present on the RXD[3:0]

lines. The signal is de-asserted at the end of the packet. The signal is valid on

the rising edge of the RXC.

Receive Data.

These are the four parallel receive data lines aligned on the nibble boundaries

driven synchronously to the RXC for reception by the external physical unit

(PHY).

Receive Error.

If a 5B decode error occurs, such as invalid /J/K/, invalid /T/R/, or invalid

symbol, this pin will go high.

Fiber/UTP Enable.

During power on reset, this pin status is latched to determine the media mode to

operate in.

1: Fiber mode

0: UTP mode

An internal weak pull low resistor sets this to the default of UTP mode. It is possible to

use an external 5.1KΩ pull high resistor to enable fiber mode.

After power on, the pin operates as the Receive Error pin.

Single-Chip/Port 10/100 Fast Ethernet PHYceiver

4

Track ID: JATR-1076-21 Rev. 1.21