RTL8139D Ver la hoja de datos (PDF) - Unspecified

Número de pieza

componentes Descripción

Lista de partido

RTL8139D Datasheet PDF : 67 Pages

| |||

RTL8139DL

Datasheet

4. Pin Descriptions

Note that some pins have multiple functions. Refer to the Pin Assignment diagrams for a graphical

representation.

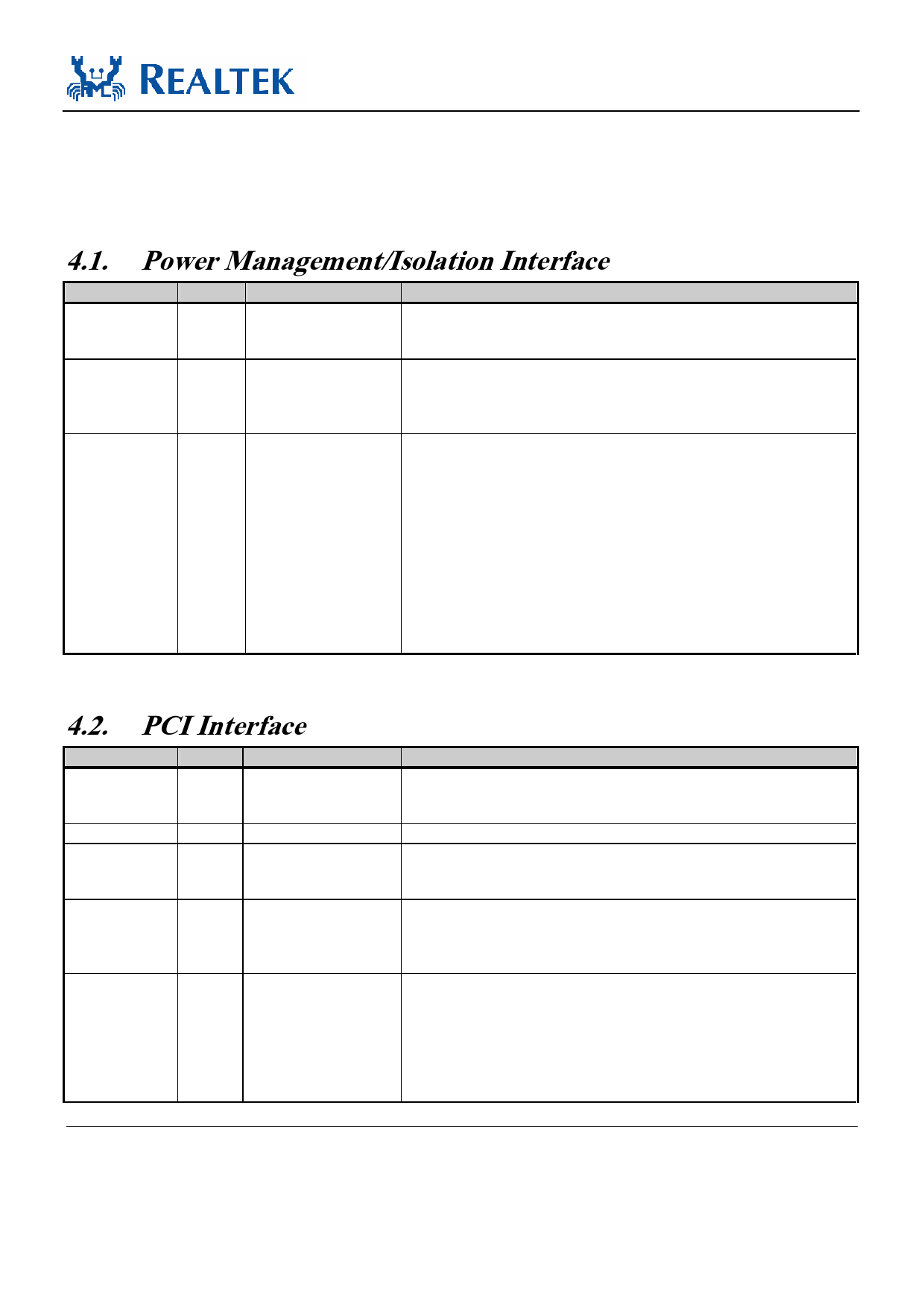

4.1. Power Management/Isolation Interface

Symbol

PMEB

(PME#)

ISOLATEB

(ISOLATE#)

Type

O/D

I

LWAKE

O

Pin No

57

74

64

Description

Power Management Event: Open drain, active low. Used by the

RTL8139D(L) to request a change in its current power management

state and/or to indicate that a power management event has occurred.

Isolate pin: Active low. Used to isolate the RTL8139D(L) from the PCI

bus. The RTL8139D(L) does not drive its PCI outputs (excluding

PME#) and does not sample its PCI input (including RST# and

PCICLK) as long as the Isolate pin is asserted.

LAN WAKE-UP signal: This signal is used to inform the motherboard

to execute the wake-up process. The motherboard must support

Wake-On-LAN (WOL). There are 4 choices of output, including active

high, active low, positive pulse, and negative pulse, that may be asserted

from the LWAKE pin. Please refer to the LWACT bit in the CONFIG1

register and the LWPTN bit in the CONFIG4 register for the setting of

this output signal. The default output is an active high signal.

Once a PME event is received, the LWAKE and PMEB assert at the

same time when the LWPME (bit4, CONFIG4) is set to 0. If the

LWPME is set to 1, the LWAKE asserts only when the PMEB asserts

and the ISOLATEB is low.

This pin is a 3.3V signaling output pin.

4.2. PCI Interface

Symbol

AD31-0

C/BE3-0

CLK

Type

T/S

T/S

I

Pin No

86,87,89,91-95,100,

1,3-5,8-10,23-30,33,

36-38,41,42,44,45

98,11,21,32

83

DEVSELB

S/T/S

15

FRAMEB

S/T/S

12

Description

PCI address and data multiplexed pins.

Pins AD31-24 are shared with BootROM data pins, while AD16-0 are

shared with BootROM address pins.

PCI bus command and byte enables multiplexed pins.

Clock: This PCI Bus clock provides timing for all transactions and bus

phases, and is input to PCI devices. The rising edge defines the start of

each phase. The clock frequency ranges from 0 to 33MHz.

Device Select: As a bus master, the RTL8139D(L) samples this signal

to insure that a PCI target recognizes the destination address for the data

transfer. As a target, the RTL8139D(L) asserts this signal low when it

recognizes its target address after FRAMEB is asserted.

Cycle Frame: As a bus master, this pin indicates the beginning and

duration of an access. FRAMEB is asserted low to indicate the start of a

bus transaction. While FRAMEB is asserted, data transfer continues.

When FRAMEB is deasserted, the transaction is in the final data phase.

As a target, the device monitors this signal before decoding the address

to check if the current transaction is addressed to it.

Single Chip Multifunction 10/100 Ethernet Controller w/Power Management 4 Track ID: JATR-1076-21 Rev. 1.2