M12L128324A-6TIG Ver la hoja de datos (PDF) - [Elite Semiconductor Memory Technology Inc.

Número de pieza

componentes Descripción

Lista de partido

M12L128324A-6TIG Datasheet PDF : 49 Pages

| |||

ESMT

M12L128324A

Operation temperature condition -40°C~85°C

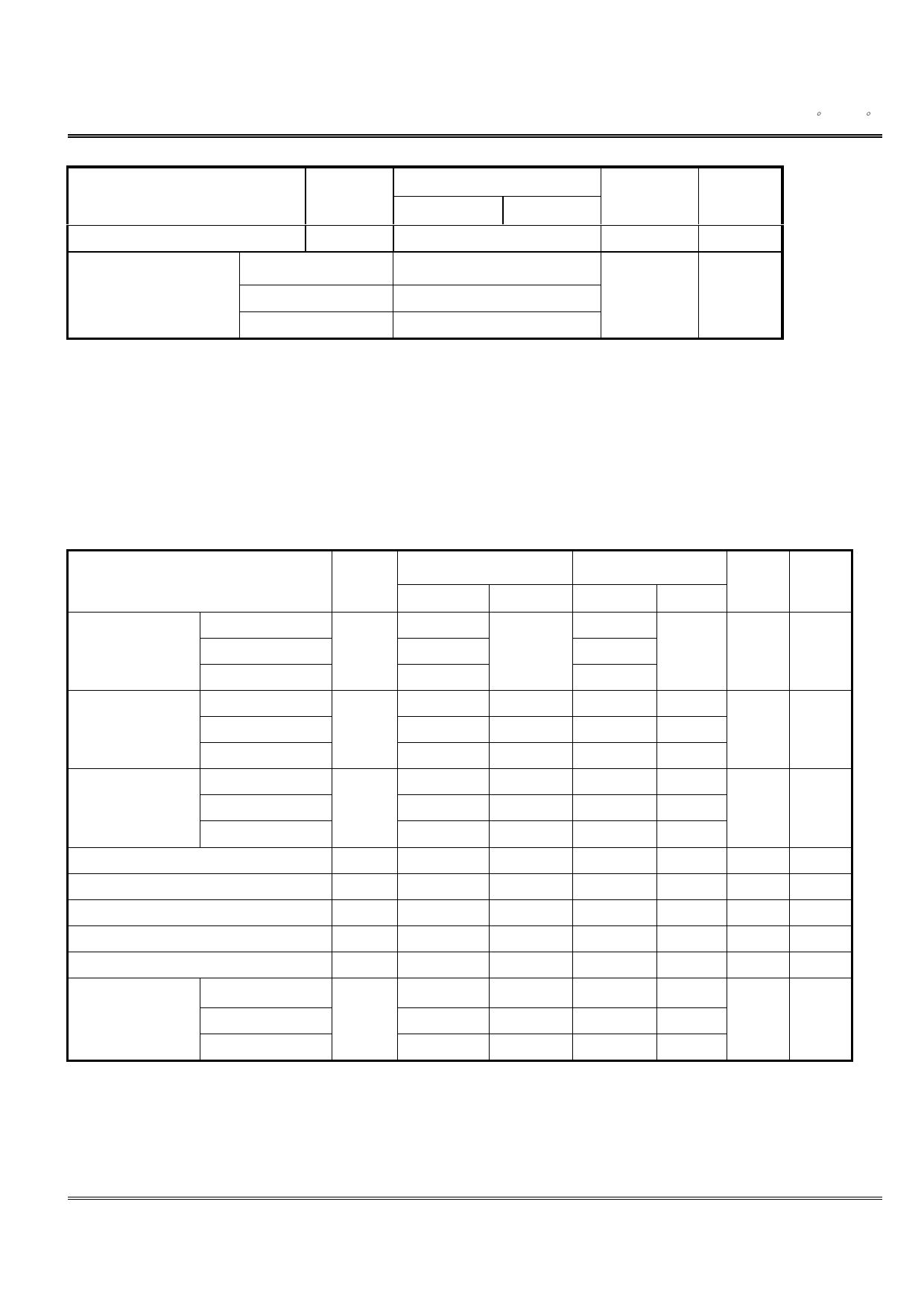

Parameter

Symbol

Col. address to col. address delay tCCD(min)

Number of valid

Output data

CAS latency = 3

CAS latency = 2

CAS latency = 1

Version

-6

-7

1

2

1

0

Unit

Note

CLK

3

ea

4

Note : 1. The minimum number of clock cycles is determined by dividing the minimum time required with clock cycle time and then

rounding off to the next higher integer.

2. Minimum delay is required to complete write.

3. All parts allow every cycle column address change.

4. In case of row precharge interrupt, auto precharge and read burst stop.

5. A new command may be given tRFC after self refresh exit.

6. A maximum of eight consecutive AUTO REFRESH commands (with tRFCmin) can be posted to any given SDRAM, and the

maximum absolute internal between any AUTO REFRESH command and the next AUTO REFRESH command is 8x15.6

μs.

AC CHARACTERISTICS (AC operating condition unless otherwise noted)

Parameter

Symbol

CAS latency = 3

CLK cycle time

CAS latency = 2

tCC

CAS latency = 1

CLK to valid

output delay

CAS latency = 3

CAS latency = 2

tSAC

CAS latency = 1

Output data

hold time

CAS latency = 3

CAS latency = 2

tOH

CAS latency = 1

CLK high pulsh width

tCH

CLK low pulsh width

tCL

Input setup time

tSS

Input hold time

tSH

CLK to output in Low-Z

tSLZ

CLK to output

in Hi-Z

CAS latency = 3

CAS latency = 2

tSHZ

CAS latency = 1

-6

Min

Max

6

10

1000

20

-

5.5

-

6

-

17

2

-

2

-

2

-

2

-

2

-

2

-

1

-

1

-

-

5.5

-

6

-

17

-7

Unit Note

Min

Max

7

8.6

1000

ns

1

20

-

6

-

6

ns

1,2

-

18

2

-

2

-

ns

2

2

-

2.5

-

ns

3

2.5

-

ns

3

2

-

ns

3

1

-

ns

3

1

-

ns

2

-

6

-

6

ns

-

-

18

Note :

1. Parameters depend on programmed CAS latency.

2. If clock rising time is longer than 1ns. (tr/2 - 0.5) ns should be considered.

3. Assumed input rise and fall time (tr & tf) =1ns.

If tr & tf is longer than 1ns. transient time compensation should be considered.

i.e., [(tr + tf)/2 – 1] ns should be added to the parameter.

Elite Semiconductor Memory Technology Inc.

Publication Date: Feb. 2006

Revision: 1.1

8/49