7480 Ver la hoja de datos (PDF) - Renesas Electronics

Número de pieza

componentes Descripción

Lista de partido

7480 Datasheet PDF : 98 Pages

| |||

PRELIMINARY NSootimcee: pTahriasmisentroict alimfinitsalasrpeescuifbicjeactitotno. change.

MITSUBISHI MICROCOMPUTERS

7480/7481 GROUP

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

FUNCTIONAL DESCRIPTION

Central Processing Unit (CPU)

The 7480/7481 group uses the standard 740 family CPU. Refer to

the table of 740 family addressing modes and machine instruc-

tions or the MELPS 740 programming manual for details on the

instruction set.

Machine-resident 740 family instructions are as follows:

1. The FST and SLW instructions are not available.

2. The MUL and DIV instructions are available.

3. The WIT instruction is available. (Note)

4. The STP instruction is available. (Note)

Note: When using these instructions, refer to the corresponding

chapter “STP and WIT instruction control” below.

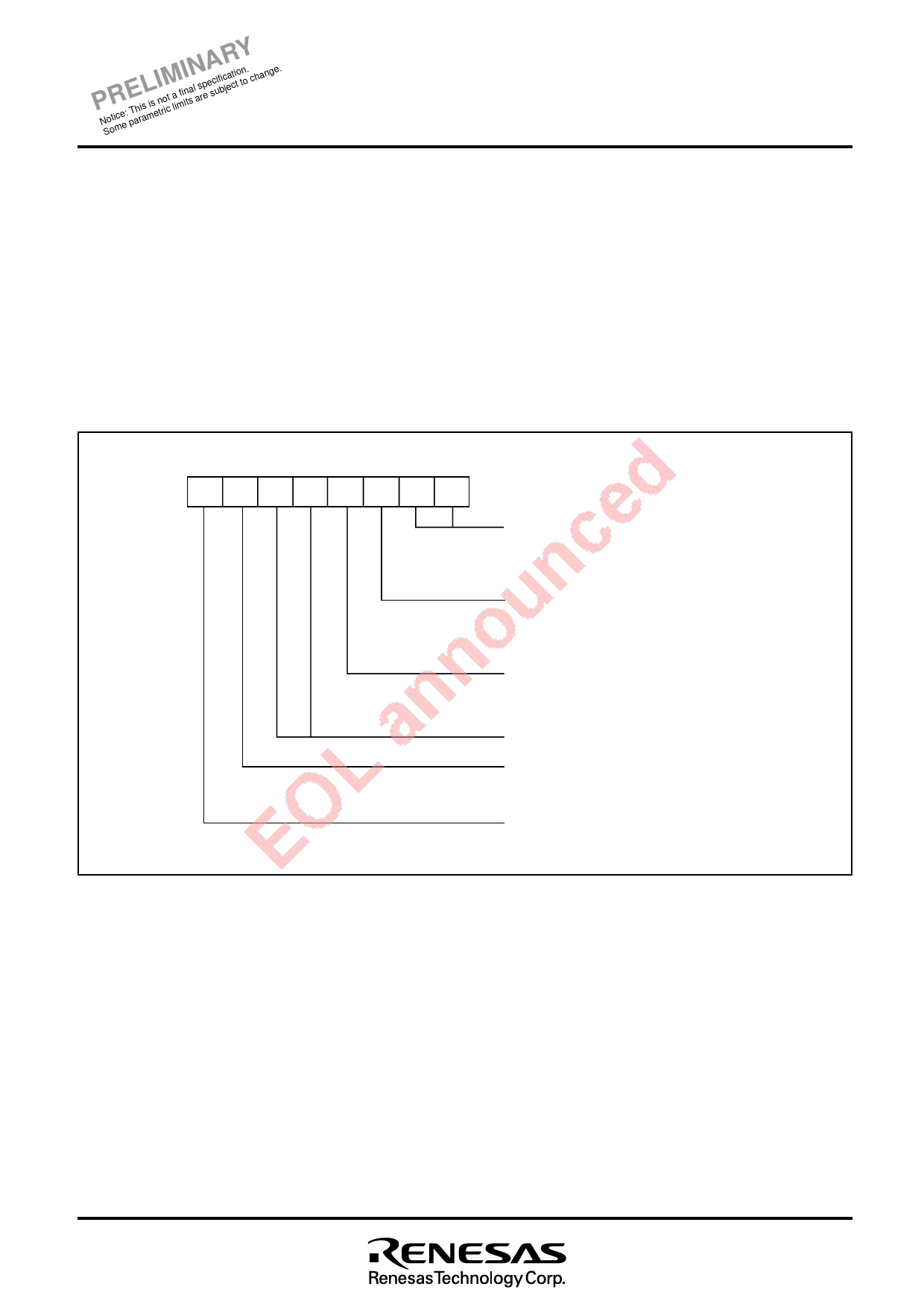

CPU Mode Register

The stack page selection bit is assigned to the CPU mode regis-

ter. This register is allocated at address 00FB16.

b7

b0

CPU mode register (CPUM: address 00FB16)

Not used.

These bits must always be set to “0”.

Stack page selection bit (Note)

0 : Page 0

1 : Page 1

Watchdog timer L count source selection bit

0 : f(XIN)/8

1 : f(XIN)/16

Not used (undefined at read)

System clock division proportion selection bit

0 : f = f(XIN)/2 (high-speed mode)

1 : f = f(XIN)/8 (medium-speed mode)

Not used (undefined at read)

Note : In the models of RAM size under 192 bytes, set this bit to “0”.

Fig. 7 Structure of CPU mode register

10