BR24G1MFVT-3AGTR(2015) Ver la hoja de datos (PDF) - ROHM Semiconductor

Número de pieza

componentes Descripción

Lista de partido

BR24G1MFVT-3AGTR

(Rev.:2015)

(Rev.:2015)

BR24G1MFVT-3AGTR Datasheet PDF : 40 Pages

| |||

BR24Gxxx-3A (128K 256K 1M)

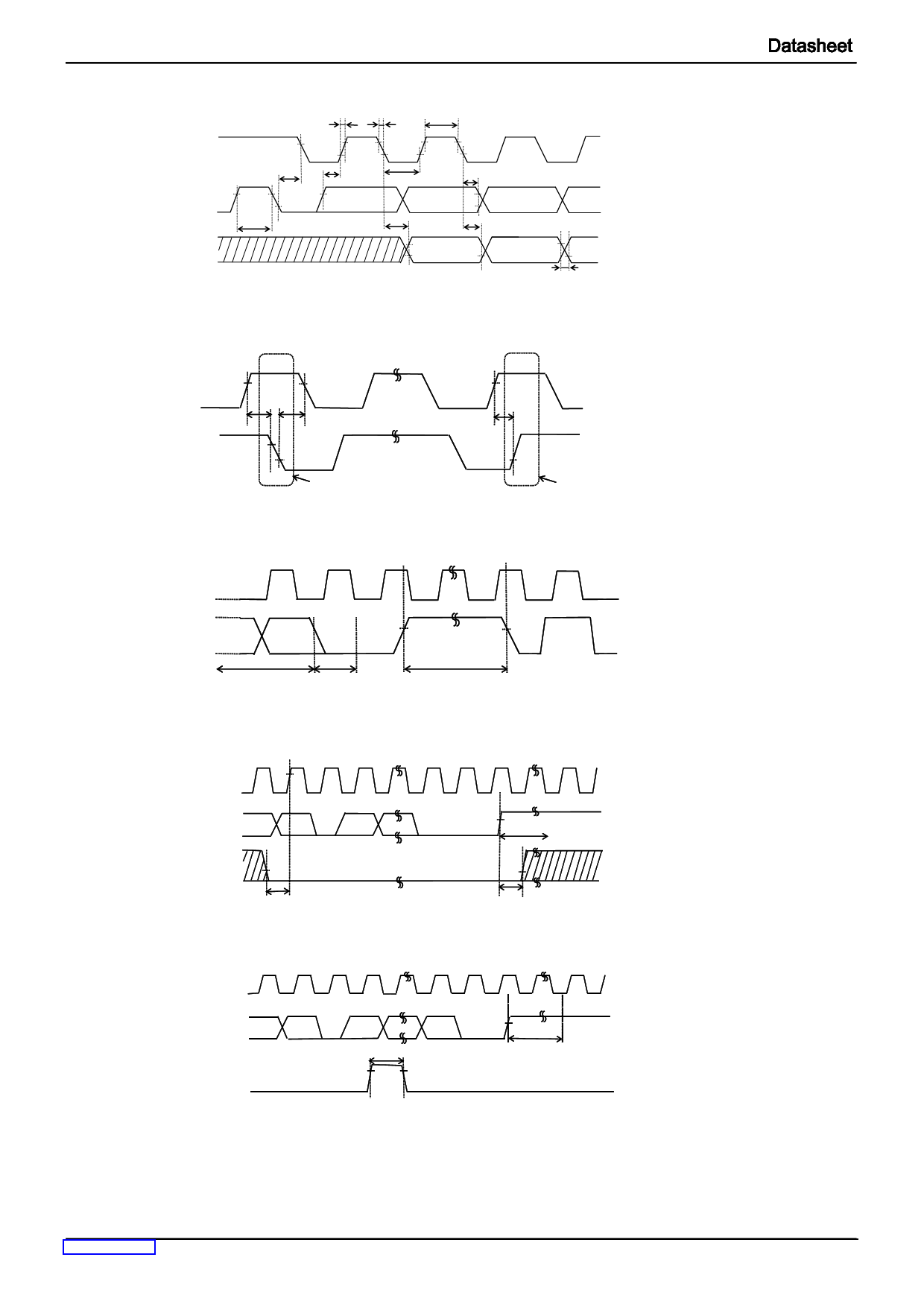

Serial Input / Output Timing

tR

tF1

tHIGH

SCL

tHD:STA

70%

70% 70%

30%

30%

tSU:DAT

tLOW

70%

30%

70%

70%

70%

SDA

(INP(入U力 T))

30%

tBUF

tPD

70%

30%

tHD:DAT

70%

30%

tDH

SDA

(OUTP(U出T力) )

70%

30%

30%

○Input read at the rise edge of SCL

○Data output in sync with the fall of SCL

70%

30%

tF2

Figure 2-(a). Serial Input / Output Timing

70%

70%

70%

tSU:STA

tHD:STA

tSU:STO

70%

30%

30%

START CONDITION

Figure 2-(b). Start-Stop Bit Timing

STOP CONDITION

D0

write data

(n-th address)

ACK

70%

70%

tWR

STOP CONDITION START CONDITION

Figure 2-(c). Write Cycle Timing

70%

DATA(1)

D1

D0 ACK

DATA(n)

ACK

70%

tWR

30%

30%

tSU:WP

tHD:WP

STOP CONDITION

Figure 2-(d). WP Timing at Write Execution

DATA(1)

D1 D0 ACK

DATA(n)

tHIGH:WP

70%

70%

ACK

70%

tWR

Figure 2-(e). WP Timing at Write Cancel

www..rohm.com

© 2014 ROHM Co., Ltd. All rights reserved.

TSZ22111・15・001

5/36

TSZ02201-0R2R0G100020-1-2

18.Jun.2015 Rev.006