CS5394 Ver la hoja de datos (PDF) - Cirrus Logic

Número de pieza

componentes Descripción

Lista de partido

CS5394 Datasheet PDF : 22 Pages

| |||

CS5394

GENERAL DESCRIPTION

The CS5394 is a 24-bit, stereo A/D converter de-

signed for stereo digital audio applications. The de-

vice uses a patented, 7th-order tri-level delta-sigma

modulator to sample the analog input signals at 64

times the output sample rate (Fs) of the device.

Sample rates of up to 50 kHz are supported. The an-

alog input channels are simultaneously sampled by

separate delta-sigma modulators. The resulting se-

rial bit streams are digitally filtered, yielding pairs

of 24-bit values. This technique yields nearly ideal

conversion performance independent of input fre-

quency and amplitude. The converter does not re-

quire difficult-to-design or expensive anti-alias

filters and it does not require external sample-and-

hold amplifiers or voltage references.

An on-chip voltage reference provides for a differ-

ential input signal range of 4.0 Vpp. The device

also contains a high pass filter, implemented digi-

tally after the decimation filter, to completely elim-

inate any internal offsets in the converter or any

offsets present at the input to the device. Output

data is available in serial form, coded as 2’s com-

plement 24-bit numbers.

For more information on delta-sigma modulation

techniques see the references at the end of this data

sheet.

SYSTEM DESIGN

Very few external components are required to sup-

port the ADC. Normal power supply decoupling

components, voltage reference bypass capacitors

and a single resistor and capacitor on each input for

isolation are all that’s required, as shown in Figure

1.

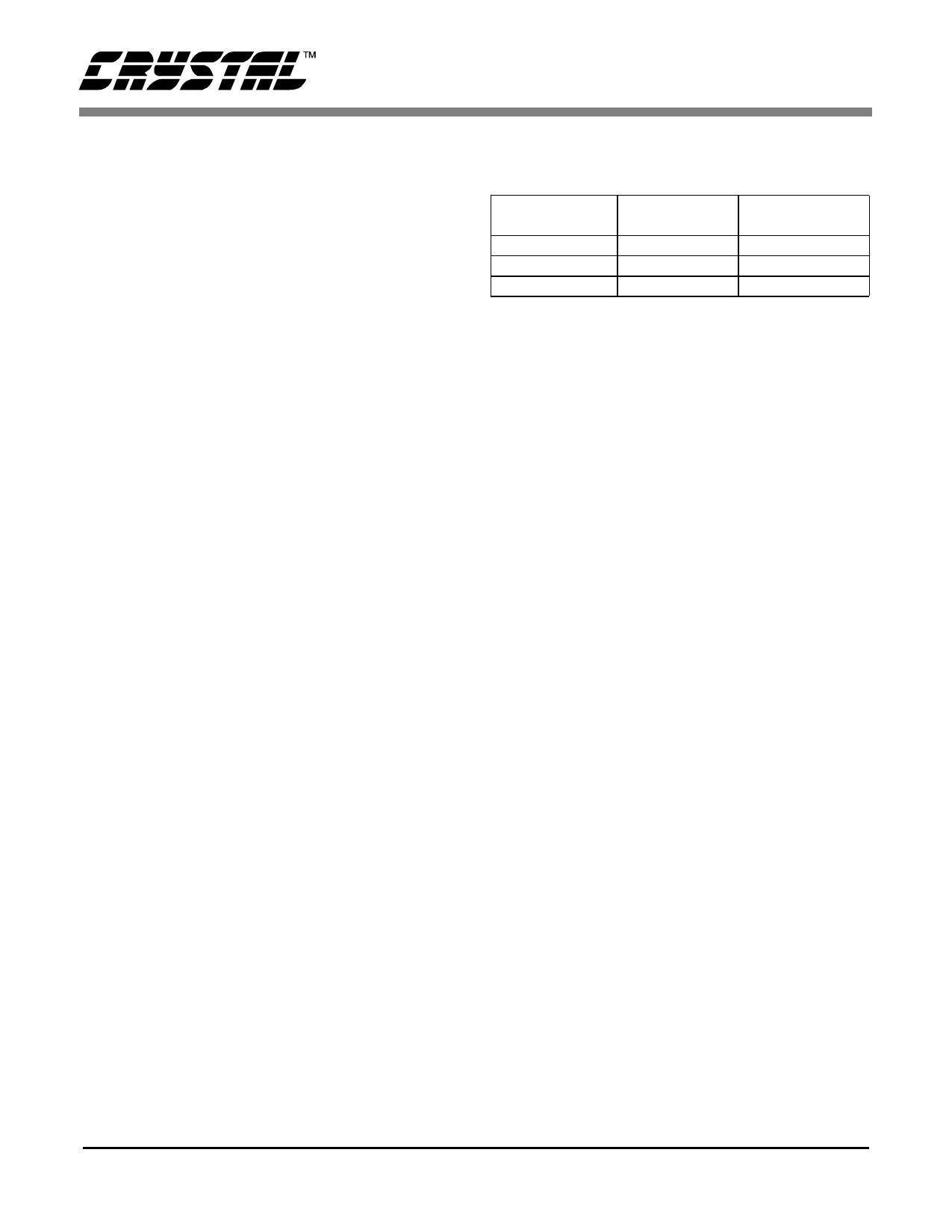

Master Clock

The master clock is the clock source for the delta-

sigma modulator (MCLKA) and digital filters

(MCLKD). The required MCLKA/D frequencies

are determined by the desired Fs and must be

256x Fs, as shown in Table 1.

LRCK

(kHz)

32

44.1

48

MCLKA/D

(MHz)

8.192

11.2896

12.288

SCLK

(MHz)

2.048

2.822

3.072

Table 1. Common Clock Frequencies

SERIAL DATA INTERFACE

The CS5394 supports two serial data formats

which are selected via the digital format select pin,

DFS. The digital format determines the relation-

ship between the serial data, left/right clock and se-

rial clock. Figures 2 and 3 detail the interface

formats. The serial data interface is accomplished

via the serial data output, SDATA, serial data

clock, SCLK, and the left/right clock, LRCK. The

serial nature of the output data results in the left and

right data words being read at different times.

However, the samples within each left/right pair

represent simultaneously sampled analog inputs.

Serial Data

The serial data block consists of 24 bits of audio

data presented in 2’s-complement format with the

MSB-first. The data is clocked from SDATA by

the serial clock and the channel is determined by

the Left/Right clock.

Serial Clock

The serial clock shifts the digitized audio data from

the internal data registers via the SDATA pin.

SCLK is an output in Master Mode where internal

dividers will divide the master clock by 4 to gener-

ate a serial clock which is 64× Fs. In Slave Mode,

SCLK is an input with a serial clock typically be-

tween 48× and 128× Fs. It is recommended that

SCLK be equal to 64× Fs, though other frequencies

are possible, to avoid potential interference effects

which may degrade system performance.

DS258PP4

9