AS7C3364PFS36A-100TQC Hoja de datos - Alliance Semiconductor

Functional description

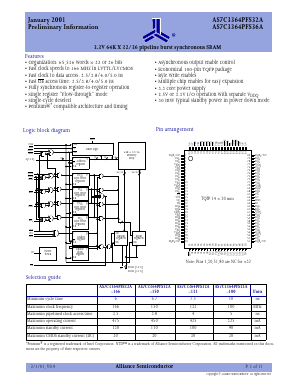

The AS7C3364PFS32A and AS7C3364PFS36A are high-performance CMOS 2-Mbit synchronous Static Random Access Memory (SRAM) devices organized as 65,536 words × 32 or 36 bits, and incorporate a two-stage register-register pipeline for highest frequency on any given technology.

FEATUREs

• Organization: 65,536 words × 32 or 36 bits

• Fast clock speeds to 166 MHz in LVTTL/LVCMOS

• Fast clock to data access: 3.5/3.8/4.0/5.0 ns

• Fast OE access time: 3.5/3.8/4.0/5.0 ns

• Fully synchronous register-to-register operation

• Single register “Flow-through” mode

• Single-cycle deselect

• Pentium®* compatible architecture and timing

• Asynchronous output enable control

• Economical 100-pin TQFP package

• Byte write enables

• Multiple chip enables for easy expansion

• 3.3 core power supply

• 2.5V or 3.3V I/O operation with separate VDDQ

• 30 mW typical standby power in power down mode