PSD4235G6V-90UII Hoja de datos - STMicroelectronics

SUMMARY DESCRIPTION

The PSD family of memory systems for microcontrollers (MCUs) brings In-System-Programmability (ISP) to Flash memory and programmable logic. The result is a simple and flexible solution for embedded designs. PSD devices combine many of the peripheral functions found in MCU based applications.

FEATURES SUMMARY

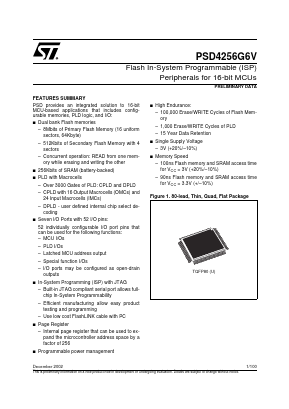

PSD provides an integrated solution to 16-bit MCU-based applications that includes configurable memories, PLD logic, and I/O:

■ Dual bank Flash memories

– 8Mbits of Primary Flash Memory (16 uniform sectors, 64Kbyte)

– 512Kbits of Secondary Flash Memory with 4 sectors

– Concurrent operation: READ from one memory while erasing and writing the other

■ 256Kbits of SRAM (battery-backed)

■ PLD with Macrocells

– Over 3000 Gates of PLD: CPLD and DPLD

– CPLD with 16 Output Macrocells (OMCs) and 24 Input Macrocells (IMCs)

– DPLD - user defined internal chip select decoding

■ Seven l/O Ports with 52 I/O pins: 52 individually configurable I/O port pins that can be used for the following functions:

– MCU I/Os

– PLD I/Os

– Latched MCU address output

– Special function I/Os

– l/O ports may be configured as open-drain outputs

■ In-System Programming (ISP) with JTAG

– Built-in JTAG compliant serial port allows fullchip In-System Programmability

– Efficient manufacturing allow easy product testing and programming

– Use low cost FlashLINK cable with PC

■ Page Register

– Internal page register that can be used to expand the microcontroller address space by a factor of 256

■ Programmable power management

■ High Endurance:

– 100,000 Erase/WRITE Cycles of Flash Memory

– 1,000 Erase/WRITE Cycles of PLD

– 15 Year Data Retention

■ Single Supply Voltage

– 3V (+20%/–10%)

■ Memory Speed

– 100ns Flash memory and SRAM access time for VCC = 3V (+20%/–10%)

– 90ns Flash memory and SRAM access time for VCC = 3.3V (+/–10%)