HS-80C86RH Ver la hoja de datos (PDF) - Intersil

Número de pieza

componentes Descripción

Lista de partido

HS-80C86RH Datasheet PDF : 29 Pages

| |||

HS-80C86RH

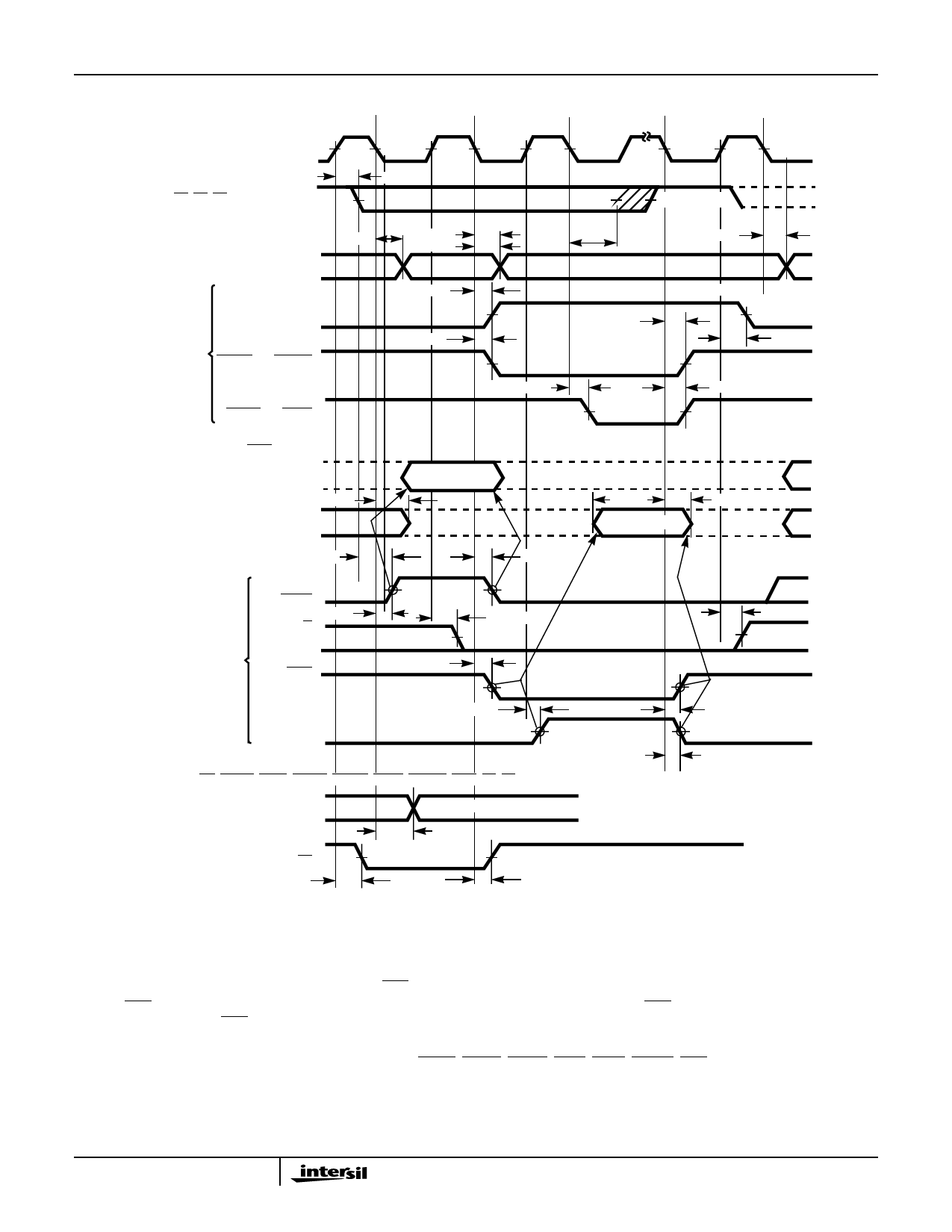

Waveforms (Continued)

T1

CLK

S2, S1, S0 (EXCEPT HALT)

TCHSV

WRITE CYCLE

AD15-AD0

TCLAV

82C88

OUTPUTS

SEE NOTES

63, 64

DEN

AMWC OR AIOWC

TCLDV

TCLAX

TCVNV

TCLML

MWTC OR IOWC

T2

T3 TW

T4

TCLSH

(SEE

NOTE 66)

TCLDX2

TCLMH

TCLML

TCVNX

TCLMH

INTA CYCLE

AD15-AD0

(SEE NOTES 61, 62)

TCLAZ

AD15-AD0

TSVMCH

RESERVED FOR

CASCADE ADDR

TCLMCL

TDVCL

POINTER

TCLDX1

MCE/PDEN

TCLMCH

DT/R

82C88 OUTPUTS

SEE NOTES 63, 64

INTA

TCLML

TCHDTL

TCHDTH

TCVNV

TCLMH

DEN

SOFTWARE

HALT - RD, MRDC, IORC, MWTC, AMWC, IOWC, AIOWC, INTA, S0, S1 = VOH

AD15-AD0

INVALID ADDRESS

TCLAV

TCVNX

S2

NOTES:

TCHSV

TCLSH

FIGURE 4. BUS TIMING - MAXIMUM MODE SYSTEM (USING 82C88)

59. All signals switch between VOH and VOL unless otherwise specified.

60. RDY is sampled near the end of T2, T3, TW to determine if TW machines states are to be inserted.

61. Cascade address is valid between first and second INTA cycle.

62. Two INTA cycles run back-to-back. The HS-80C86RH local ADDR/DATA bus is inactive during both INTA cycles. Control for pointer address is

shown for the second INTA cycle.

63. Signals at HS-82C85RH or 82C88 are shown for reference only.

64. The issuance of the 82C88 command and control signals (MRDC, MWTC, AMWC, IORC, IOWC, AIOWC, INTA and DEN) lags the active high

82C88 CEN.

65. All timing measurements are made at 1.5V unless otherwise noted.

66. Status inactive in state just prior to T4.

14