RTL8198 Ver la hoja de datos (PDF) - Realtek Semiconductor

Número de pieza

componentes Descripción

Lista de partido

RTL8198 Datasheet PDF : 86 Pages

| |||

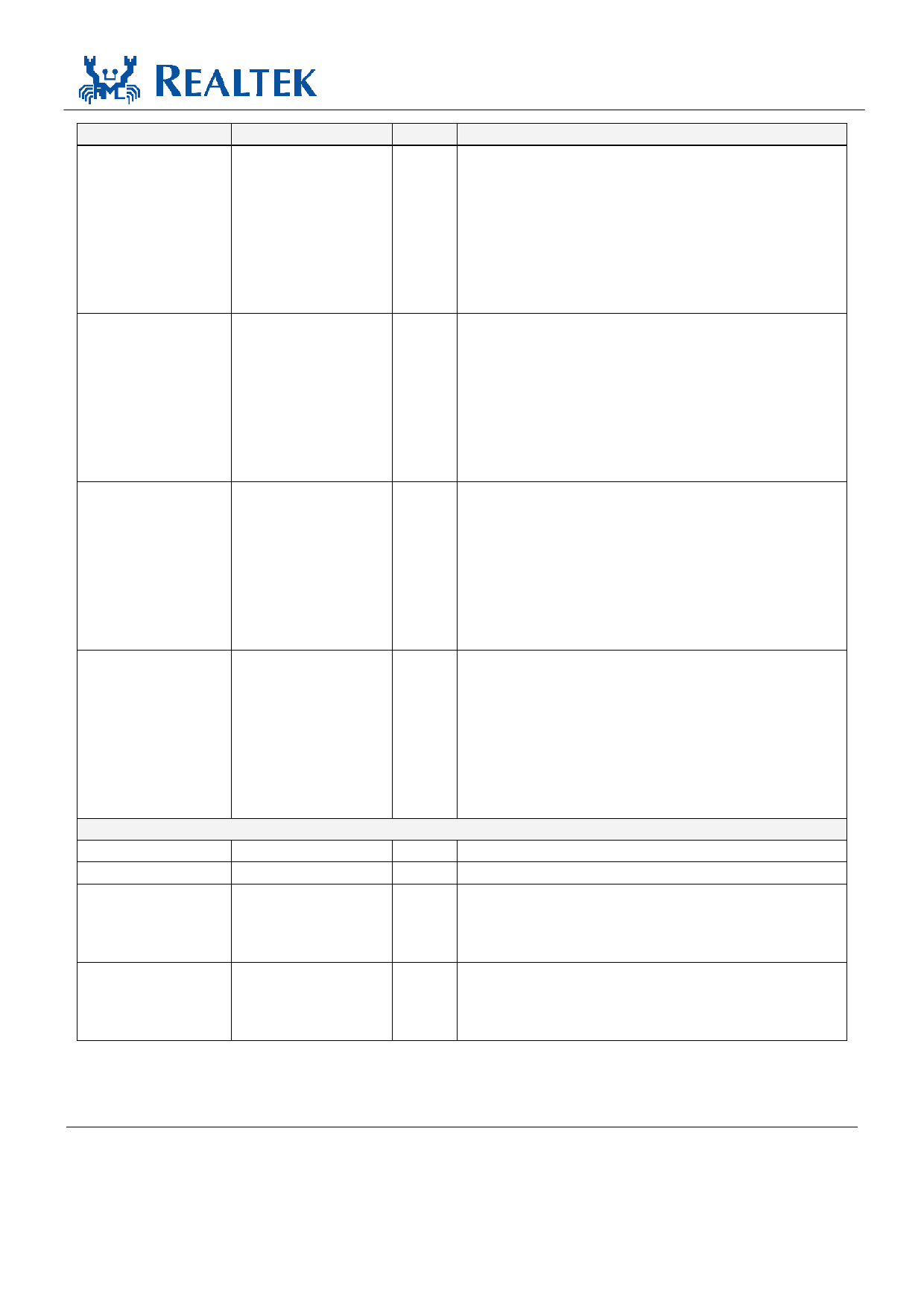

Pin Name

P1MDIAP/N

P1MDIBP/N

P1MDICP/N

P1MDIDP/N

P2MDIAP/N

P2MDIBP/N

P2MDICP/N

P2MDIDP/N

P3MDIAP/N

P3MDIBP/N

P3MDICP/N

P3MDIDP/N

P4MDIAP/N

P4MDIBP/N

P4MDICP/N

P4MDIDP/N

MDC

MDIO

P5_GTXC

P5_TXC

RTL8198

Datasheet

Pin No.

Type Description

66

AI/O Port1 Media Dependent Interface A~D. For 1000Base-T

67

operation, differential data from the media is transmitted and

69

received on all four pairs. For 100Base-Tx and 10Base-T

70

operation, only MDIAP/N and MDIBP/N are used. Auto

MDIX can reverse the pairs MDIAP/N and MDIBP/N.

72

73

Each of the differential pairs has an internal 100 ohm

74

termination resistor.

75

79

AI/O Port2 Media Dependent Interface A~D. For 1000Base-T

80

operation, differential data from the media is transmitted and

82

received on all four pairs. For 100Base-Tx and 10Base-T

83

operation, only MDIAP/N and MDIBP/N are used. Auto

MDIX can reverse the pairs MDIAP/N and MDIBP/N.

85

86

Each of the differential pairs has an internal 100 ohm

87

termination resistor.

88

90

AI/O Port3 Media Dependent Interface A~D. For 1000Base-T

91

operation, differential data from the media is transmitted and

93

received on all four pairs. For 100Base-Tx and 10Base-T

94

operation, only MDIAP/N and MDIBP/N are used. Auto

MDIX can reverse the pairs MDIAP/N and MDIBP/N.

96

97

Each of the differential pairs has an internal 100 ohm

98

termination resistor.

99

101

AI/O Port4 Media Dependent Interface A~D. For 1000Base-T

102

operation, differential data from the media is transmitted and

104

received on all four pairs. For 100Base-Tx and 10Base-T

105

operation, only MDIAP/N and MDIBP/N are used. Auto

MDIX can reverse the pairs MDIAP/N and MDIBP/N.

107

108

Each of the differential pairs has an internal 100 ohm

109

termination resistor.

110

Ethernet MAC GMII/RGMII/MII Interface

120

O Management Data Clock.

119

IPU/O Management Data I/O.

131

O Shared for (1) MII Mode (2) GMII/RGMII Mode (3) MII

PHY Mode.

For details see section 5.2.1 MAC Interface

MII/GMII/RGMII Mode Pin Sharing Mappings, page 15.

132

I Shared for (1) MII Mode (2) GMII/RGMII Mode (3) MII

PHY Mode.

For details see section 5.2.1 MAC Interface

MII/GMII/RGMII Mode Pin Sharing Mappings, page 15.

IEEE 802.11n Gigabit Ethernet AP/Router Network Processor

8

Track ID: JATR-2265-11 Rev. 0.91