DM9102F Ver la hoja de datos (PDF) - Davicom Semiconductor, Inc.

Número de pieza

componentes Descripción

Lista de partido

DM9102F Datasheet PDF : 63 Pages

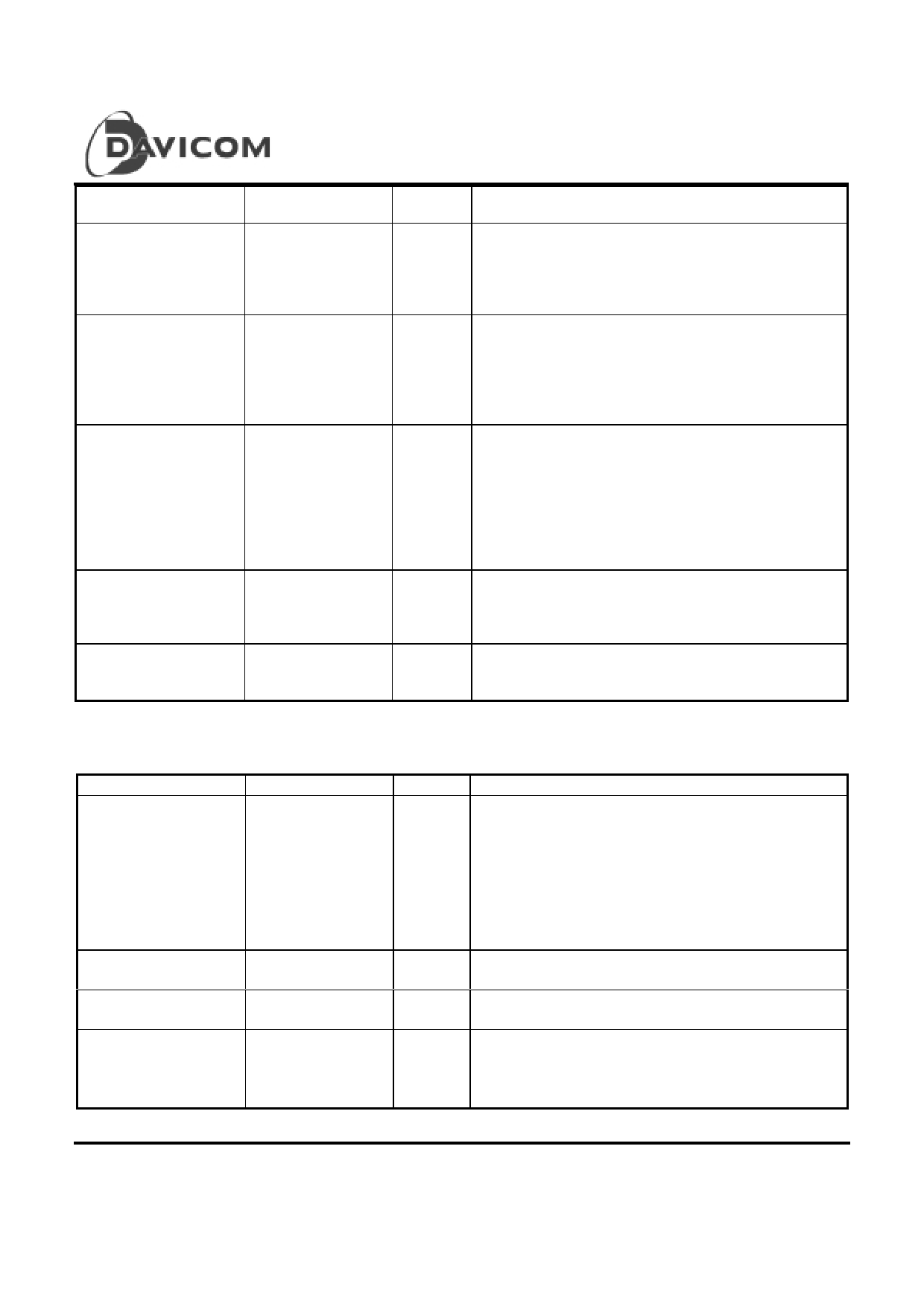

| |||

44

PAR

19

33

45

60

9~12, 14~17,

22~25,27~30,47,48,

49,52,53,56,57,58,62,

63,64,67,68,71,72,73

C/BE3#

C/BE2#

C/BE1#

C/BE0#

AD31~AD0

127

INT#

128

RST#

DM9102

10/100Mbps Single Chip LAN Controller

enabled. The system error asserts two clock cycles after

the falling address if an address parity error is detected.

I/O Parity

This signal indicates even parity across AD0~AD31 and

C/BE0#~C/BE3# including the PAR pin. This signal is an

output for the master and an input for the slave device. It is

stable and valid one clock after the address phase.

I/O Bus Command/Byte Enable

During the address phase, these signals define the bus

command or the type of bus transaction that will take

place. During the data phase these pins indicate which

byte lanes contain valid data. C/BE0# applies to bit7-0 and

C/BE3# applies to bit31-24.

I/O Address & Data

These are multiplexed address and data bus signals. As a

bus master, the DM9102 will drive address during the first

bus phase. During subsequent phases, the DM9102 will

either read or write data expecting the target to increment

its address pointer. As a target, the DM9102 will decode

each address on the bus and respond if it is the target

being addressed.

O/D Interrupt Request

This signal will be asserted low when an interrupt condition

as defined in CR5 is set, and the corresponding mask bit

in CR7 is not set.

I

System Reset

When this signal is asserted low, DM9102 performs the

internal system reset to its initial state.

Boot ROM and EEPROM Interface (Including Multiplex Mode or Direct Mode):

Multiplex Mode:

Pin No.

Pin Name

I/O

Description

75~82

BPAD0~BPAD7

I/O Boot ROM Address and Data bus

Boot ROM address and Data multiplexed lines bits

0~7. In two consecutive address cycles, these lines

contain the boot ROM address pins 7~2, out_enable

and write_enable of boot ROM in the first cycle; and

these lines contain address pins 15~8 in second cycle.

After the first two cycles, these lines contain data bit

7~0 in consective cycles.

83

BPCS#

O Boot ROM Chip Select

Boot ROM or external register chip select signal.

85

BPA0

O,LI Boot ROM address line.

Low address bit0 interfacing to Boot ROM.

86

BPA1/TEST

O Boot ROM address line.

Low address bit1 interfacing to Boot ROM.

This bit is also set to enable TEST mode only in

multiplex mode. (debug only)

Final

7

Version: DM9102-DS-F3

August 30, 2000