LPC47N227TQFP Ver la hoja de datos (PDF) - SMSC -> Microchip

Número de pieza

componentes Descripción

Lista de partido

LPC47N227TQFP Datasheet PDF : 202 Pages

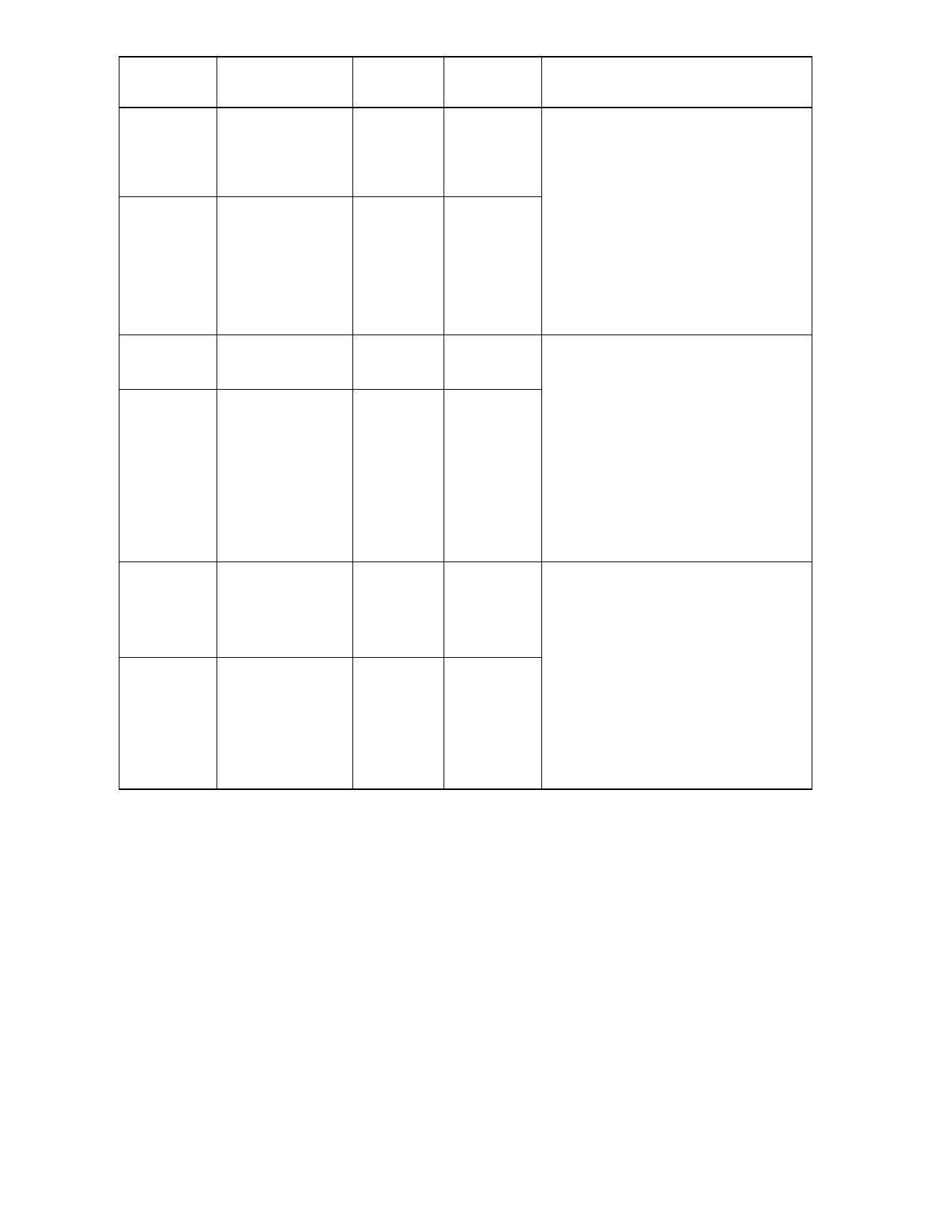

| |||

TQFP/STQFP

PIN #

NAME

86

Data Set

Ready 1

SYMBOL

nDSR1

97

Data Set

Ready 2

nDSR2

87

Request to Send 1 nRTS1

98

Request to Send 2 nRTS2

BUFFER

TYPE PER

FUNCTION1

I

I

O6

O6

DESCRIPTION

Active low Data Set Ready inputs for the

serial port. Handshake signal which

notifies the UART that the modem is ready

to establish the communication link. The

CPU can monitor the status of nDSR

signal by reading bit 5 of Modem Status

Register (MSR). A nDSR signal state

change from low to high after the last MSR

read will set MSR bit 1 to a 1. If bit 3 of

Interrupt Enable Register is set, the

interrupt is generated when nDSR

changes state.

Note: Bit 5 of MSR is the complement of

nDSR.

Active low Request to Send outputs for the

Serial Port. Handshake output signal

notifies modem that the UART is ready to

transmit data. This signal can be

programmed by writing to bit 1 of the

Modem Control Register (MCR). The

hardware reset will reset the nRTS signal

to inactive mode (high). nRTS is forced

inactive during loop mode operation.

88

Clear to

Send 1

99

Clear to

Send 2

nCTS1

nCTS2

I

Active low Clear to Send inputs for the

serial port. Handshake signal which

notifies the UART that the modem is ready

to receive data. The CPU can monitor the

status of nCTS signal by reading bit 4 of

Modem Status Register (MSR). A nCTS

I

signal state change from low to high after

the last MSR read will set MSR bit 0 to a 1.

If bit 3 of the Interrupt Enable Register is

set, the interrupt is generated when nCTS

changes state. The nCTS signal has no

effect on the transmitter.

Note: Bit 4 of MSR is the complement of

nCTS.

7