COM20022I Ver la hoja de datos (PDF) - SMSC -> Microchip

Número de pieza

componentes Descripción

Lista de partido

COM20022I Datasheet PDF : 88 Pages

| |||

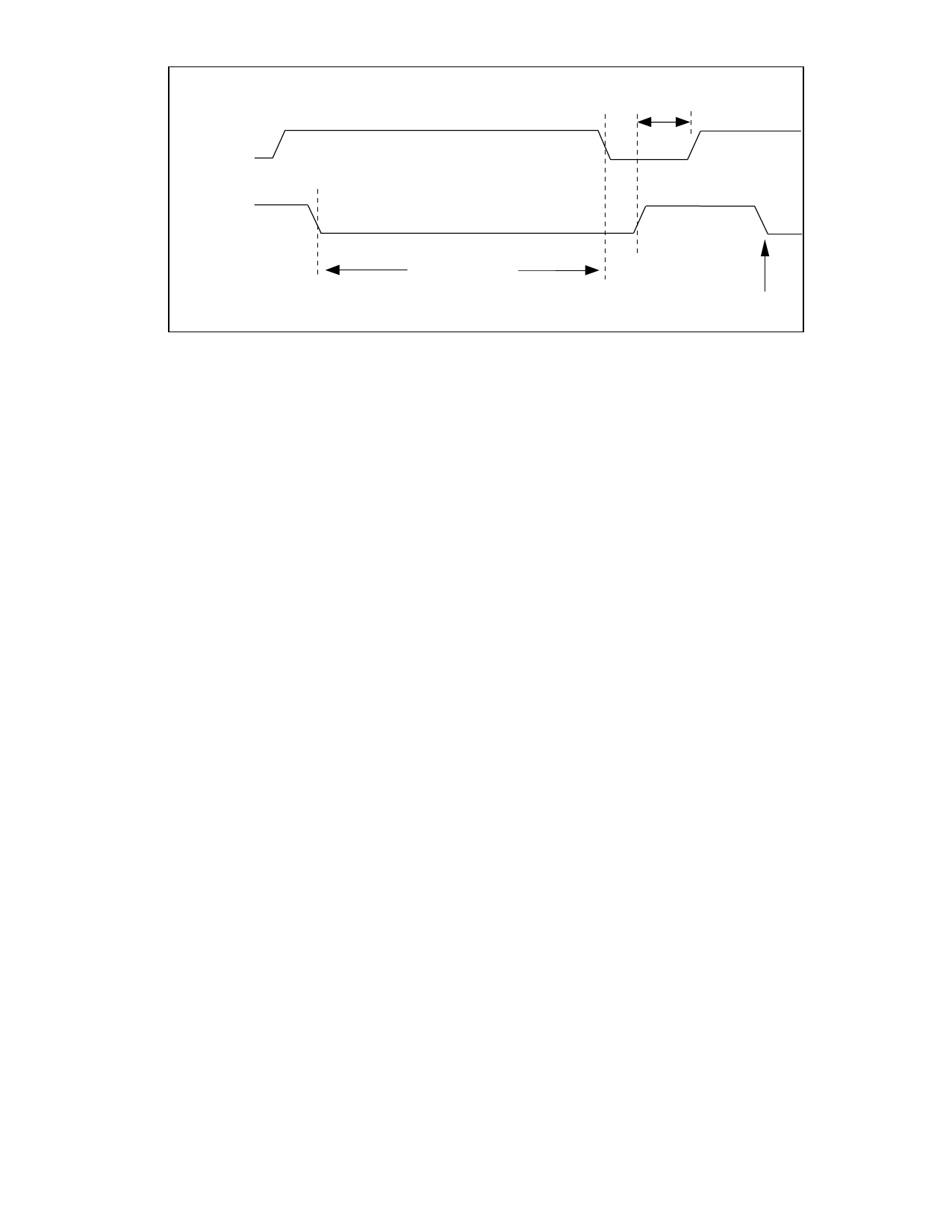

DREQ

(Active-High)

Gate

Time

nDACK

(Active-Low)

Transfer term

(Counting Read/Write pulse

or counting internal timer)

Restart

Transfer

FIGURE 5 - PROGRAMMABLE BURST MODE DMA TRANSFER (ROUGH TIMING)

The timing of the Non-Burst mode DMA data

transfer is found in the Timing Diagrams section

of this data sheet. The basic sequence of

operation is as follows:

!" nDACK becomes active (low) upon DREQ

becoming active (high) and catching the

host bus (AEN=1).

!" DREQ becomes inactive after nDACK and

read/write signal become active.

!" DREQ becomes active after nDACK or

read/write signal becomes inactive.

!" DREQ becomes inactive after TC and the

read/write signal assert (when nDACK=0).

In this case, DREQ doesn't become active

again after nDACK becomes inactive.

!" nDACK becomes inactive after DREQ=0

and the present cycle finishes.

20