FDC87W22 Ver la hoja de datos (PDF) - SMSC -> Microchip

Número de pieza

componentes Descripción

Lista de partido

FDC87W22 Datasheet PDF : 140 Pages

| |||

Game Port/Power Down Interface

If Bit 3 of CR16 (GMDRQ) is 1, Bit 4 of CR3

(GMODS0) determines whether the game port is

in Adapter mode or Portable mode (default is

Adapter mode). If Bit 3 of CR16 is 0, pin 39 and

41 are used for DMA A operation.

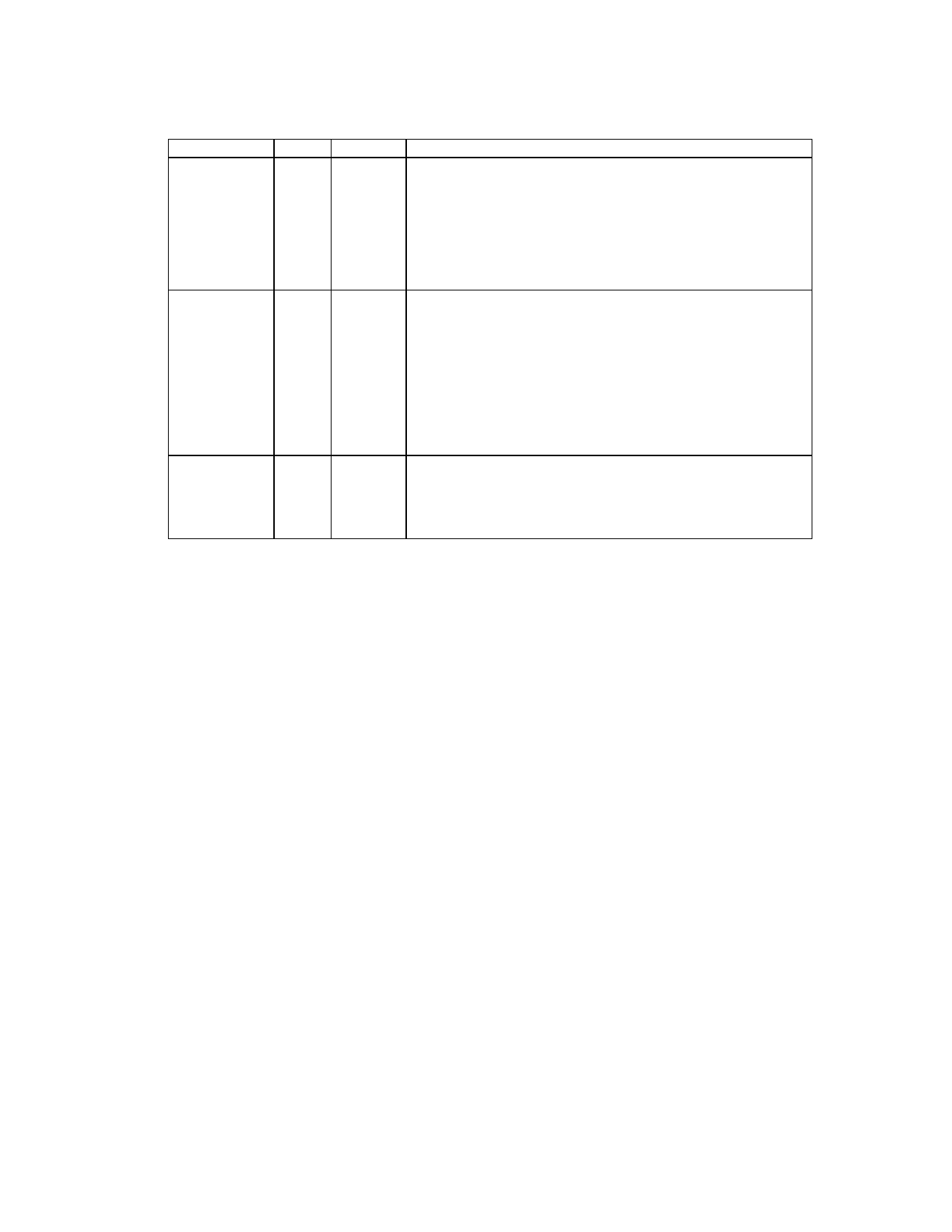

SYMBOL

nGMRD

PFDCEN

nDACK_A

nGMWR

PEXTEN

DRQ_A

PDCIN

PIN

I/O

FUNCTION

41

OUT8t When CR16 Bit 3 (GMDRQ) = 1:

OUT8t Adapter mode: Game port read control signal.

Portable mode: When parallel port is selected as Extension

FDD/Extension 2FDD mode, this pin will be active. The active

INt

state is dependent on bit 7 of CRA (PFDCACT), and default is

low active.

When CR16 Bit 3 (GMDRQ) = 0:

DMA acknowledge signal A.

39

OUT8t When CR16 Bit 3 (GMDRQ) = 1:

OUT8t Adapter mode: Game port write control signal.

Portable mode: When a particular extended mode is selected

for the parallel port, this pin will be active. The extended

modes include Extension Adapter mode, EPP mode, ECP

mode, and ECP/EPP mode, which are selected using bit 3 -

bit 0 of CRA. The active state is dependent on bit 6 of CRA

OUT8t (PEXTACT); the default is low active.

When CR16 Bit 3 (GMDRQ) = 0:

DMA request signal A.

3

INc This input pin controls the chip power down. When this pin is

active, the clock supply to the chip will be inhibited and the

output pins will be tri-stated as defined in CR4 and CR6. The

PDCIN is pulled down internally. Its active state is defined by

bit 4 of CRA (PDCHACT). Default is high active.

9